# bgyond breakpoints A Tour of Dynamic Analysis

Nathan Taylor, Fastly http://nathan.dijkstracula.net @dijkstracula

#

#### T. Ball: The Concept of Dynamic Analysis ESEC '99

#### The Concept of Dynamic Analysis

Thomas Ball

Bell Laboratories

Lucent Technologies

tball@research.bell-labs.com

**Abstract.** Dynamic analysis is the analysis of the properties of a running program. In this paper, we explore two new dynamic analyses based on program profiling:

- Frequency Spectrum Analysis. We show how analyzing the frequencies of program entities in a single execution can help programmers to decompose a program, identify related computations, and find computations related to specific input and output characteristics of a program.

- Coverage Concept Analysis. Concept analysis of test coverage data computes dynamic analogs to static control flow relationships such as domination, postdomination, and regions. Comparison of these dynamically computed relationships to their static counterparts can point to areas of code requiring more testing and can aid programmers in understanding how a program and its test sets relate to one another.

#### 1 Introduction

Dynamic analysis is the analysis of the properties of a running program. In contrast to static analysis, which examines a program's text to derive properties that hold for all executions, dynamic analysis derives properties that hold for one or more executions by examination of the running program (usually through program instrumentation [14]). While dynamic analysis cannot prove that a program satisfies a particular property, it can detect violations of properties as well as provide useful information to programmers about the behavior of their programs, as this paper will show.

The usefulness of dynamic analysis derives from two of its essential characteristics:

Precision of information: dynamic analysis typically involves instrumenting a program to examine or record certain aspects of its run-time state. This instrumentation can be tuned to collect precisely the information needed "Dynamic analysis is the analysis of the properties of a running program [...] (usually through program instrumentation)."

From Pin: Building Customized Program Analysis Tools with Dynamic Instrumentation

## classic use-cases

- Debugging a program crash or race condition

- Input to understand a new codebase

- Analysis of obfuscated software or malware

### who cares

- Huge gulf between what tools practitioners use in industry, and academic dynamic analysis work

- Many techniques shared with other cool areas like OS virtualization and compiler theory

- Techniques have different performance tradeoffs; knowing the lay of the land will help you choose the right tool for your problem

## dynamic vs static analysis

- Static analysis is a conservative approximation of runtime behavior

- Programs are only partially known (dynamic linking; user input)

- Imprecise: consider a program that typechecks but still has a bug

- Language specifications often assume a single thread of execution (or, don't specify at all): "valid" programs can still allow race conditions!

## can't prove correctness

but can demonstrate failure

## today's topics

- Pomniscient Debugging and State Tracking

- Analyzing Concurrent Systems

- Areas of Future Work

## for each topic...

- What open-source tooling exists?

- PHow does it work under the hood?

- What contributions has academia made?

→ /tmp gcc foo.c

```

→ /tmp gcc foo.c

→ /tmp ./a.out

[1] 4233 segmentation fault ./a.out

```

```

→ /tmp gcc foo.c

→ /tmp ./a.out

[1]     4233 segmentation fault ./a.out

→ /tmp gcc -g foo.c

→ /tmp gdb ./a.out

GNU gdb (Ubuntu 7.7.1-0ubuntu5~14.04.2) 7.7.1

Copyright (C) 2014 Free Software Foundation, Inc. (gdb) run

```

```

→ /tmp gcc foo.c

→ /tmp ./a.out

[1] 4233 segmentation fault ./a.out

→ /tmp gcc -g foo.c

→ /tmp gdb ./a.out

GNU gdb (Ubuntu 7.7.1-0ubuntu5~14.04.2) 7.7.1

Copyright (C) 2014 Free Software Foundation, Inc.

(gdb) run

Starting program: /tmp/a.out

```

```

Program received signal SIGSEGV, Segmentation fault. 0x000000000004004fd in baz () at foo.c:5

*foo = 42;

```

```

Program received signal SIGSEGV, Segmentation fault.

0x0000000000004004fd in baz () at foo.c:5

*foo = 42;

5

(gdb) bt

#0 0x0000000000004004fd in baz () at foo.c:5

#1 0x000000000000400513 in bar () at foo.c:9

#2 0x000000000000400523 in foo () at foo.c:13

#3 0x00000000000040053e in main (argc=1, argv=0x7fffffffe438) at foo.c:17

(gdb) inf loc

foo = 0x7

(gdb)

```

Starting program: /tmp/a.out

;login Nov 2013

#### The Night Watch

JAMES MICKENS

James Mickens is a researcher in the Distributed Systems group at Microsoft's Redmond lab. His current research focuses on web applications.

with an emphasis on the design of JavaScript frameworks that allow developers to diagnose and fix bugs in widely deployed web applications. James also works on fast, scalable storage systems for datacenters. James received his PhD in computer science from the University of Michigan, and a bachelor's degree in computer science from Georgia Tech. mickens@microsoft.com

s a highly trained academic researcher, I spend a lot of time trying to advance the frontiers of human knowledge. However, as someone who was born in the South, I secretly believe that true progress is a fantasy, and that I need to prepare for the end times, and for the chickens coming home to roost, and fast zombies, and slow zombies, and the polite zombies who say "sir" and "ma'am" but then try to eat your brain to acquire your skills. When the revolution comes, I need to be prepared; thus, in the quiet moments, when I'm not producing incredible scientific breakthroughs, I think about what I'll do when the weather forecast inevitably becomes RIVERS OF BLOOD ALL DAY EVERY DAY. The main thing that I ponder is who will be in my gang, because the likelihood of post-apocalyptic survival is directly related to the size and quality of your rag-tag group of associates. There are some obvious people who I'll need to recruit: a locksmith (to open doors); a demolitions expert (for when the locksmith has run out of ideas); and a person who can procure, train, and then throw snakes at my enemies (because, in a world without hope, snake throwing is a reasonable way to resolve disputes). All of these people will play a role in my ultimate success as a dystopian warlord philosopher. However, the most important person in my gang will be a systems programmer. A person who can debug a device driver or a distributed system is a person who can be trusted in a Hobbesian nightmare of breathtaking scope; a systems programmer has seen the terrors of the world and understood the intrinsic horror of existence. The systems programmer has written drivers for buggy devices whose firmware was implemented by a drunken child or a sober goldfish. The systems programmer has traced a network problem across eight machines, three time zones, and a brief diversion into Amish country, where the problem was transmitted in the front left hoof of a mule named Deliverance. The systems programmer has read the kernel source, to better understand the deep ways of the universe, and the systems programmer has seen the comment in the scheduler that says "DOES THIS WORK LOL," and the systems programmer has wept instead of LOLed, and the systems programmer has submitted a kernel patch to restore balance to The Force and fix the priority inversion that was causing MySQL to hang. A systems programmer will know what to do when society breaks down, because the systems programmer already lives in a world without law.

Listen: I'm not saying that other kinds of computer people are useless. I believe (but cannot prove) that PHP developers have souls. I think it's great that database people keep trying to improve select-from-where, even though the only queries that cannot be expressed using select-from-where are inappropriate limericks from "The Canterbury Tales." In some way that I don't yet understand, I'm glad that theorists are investigating the equivalence between five-dimensional Turing machines and Edward Scissorhands. In most situations, GUI designers should not be forced to fight each other with tridents and nets as I yell "THERE ARE NO MODAL DIA-LOGS IN SPARTA." I am like the Statue of Liberty: I accept everyone, even the wretched and the huddled and people who enjoy Haskell. But when things get tough, I need mission-critical people; I need a person who can wear night-vision goggles and descend from a helicopter on ropes and do classified things to protect my freedom while country music plays in the background. A systems person can do that. I can realistically give a kernel hacker a nickname like "Diamondback" or "Zeus Hammer." In contrast, no one has ever said, "These semitransparent icons are really semi-transparent! IS THIS THE

using chewing tobacco. As a systems hacker, you must be prepared to do savage things, unspeakable things, to kill runaway threads with your bare hands, to write directly to network ports using telnet and an old copy of an RFC that you found in the Vatican. When you debug systems code, there are no highlevel debates about font choices and the best kind of turquoise, because this is the Old Testament, an angry and monochromatic world, and it doesn't matter whether your Arial is Bold or Condensed when people are covered in boils and pestilence and Egyptian pharaoh oppression. HCI people discover bugs by receiving a concerned email from their therapist. Systems people discover bugs by waking up and discovering that their first-born children are missing and "ETIMEDOUT" has been written in blood on the wall.

What is despair? I have known it—hear my song. Despair is when you're debugging a kernel driver and you look at a memory dump and you see that a pointer has a value of 7. THERE IS NO HARDWARE ARCHITECTURE THAT IS ALIGNED ON 7. Furthermore, 7 IS TOO SMALL AND ONLY EVIL CODE WOULD TRY TO ACCESS SMALL NUMBER MEMORY.

Misaligned, small-number memory accesses have stolen

"Despair is when you're debugging a kernel driver and you look at a memory dump and you see that a pointer has a value of 7. THERE IS NO HARDWARE ARCHITECTURE THAT IS ALIGNED ON 7. Furthermore, 7 IS TOO SMALL AND ONLY EVIL CODE WOULD TRY TO ACCESS SMALL NUMBER MEMORY."

```

(gdb) run

Starting program: /tmp/a.out

Program received signal SIGSEGV, Segmentation fault.

0x0000000000004004fd in baz () at foo.c:5

*foo = 42;

(gdb) bt

#0 0x000000000004004fd in baz () at foo.c:5

#1 0x00000000000400513 in bar () at foo.c:9

#2 0x00000000000400523 in foo () at foo.c:13

#3 0 \times 0000000000000000053e in main (argc=1, argv=0 \times 7ffffffe438)

(gdb) inf loc

foo = 0x7

(gdb)

```

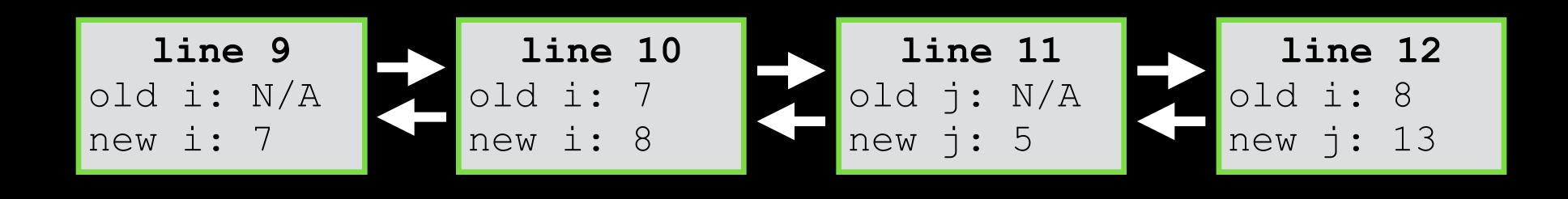

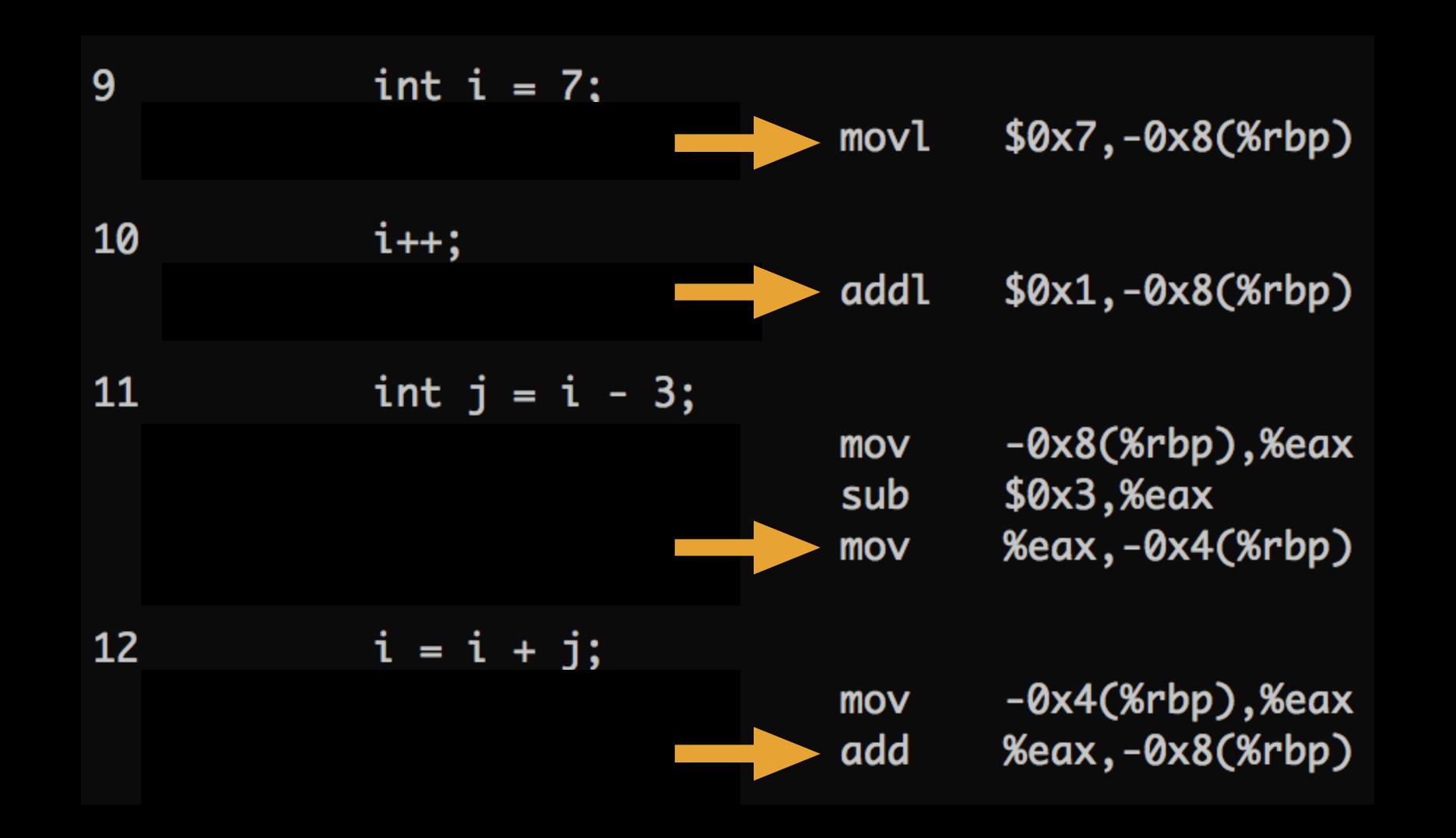

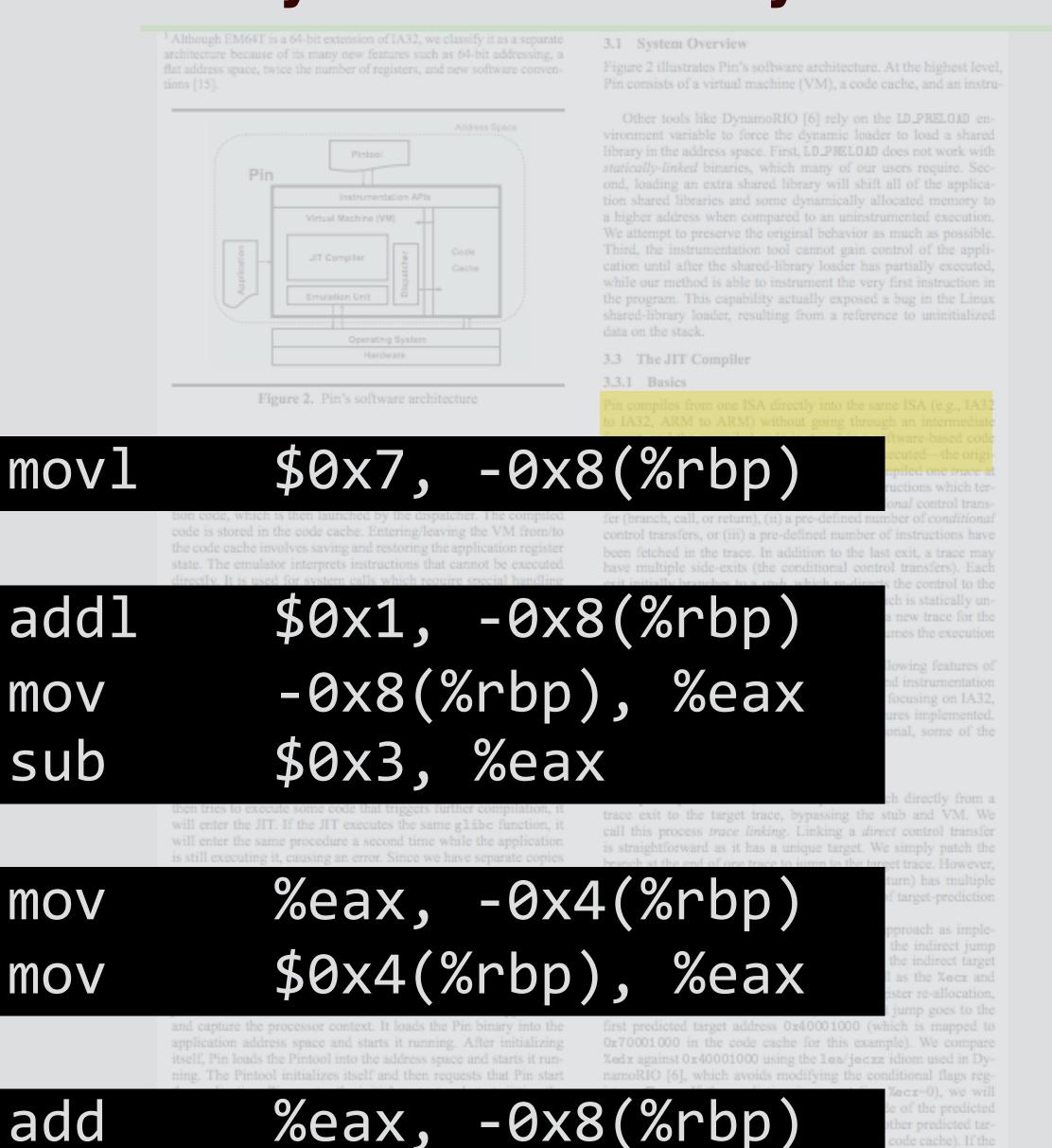

# Time-Traveling Debugging

```

int i = 7;

9

10

i++;

11

int j = i - 3;

12

i = i + j;

int i = 7:

$0x7,-0x8(%rbp)

movl

i++;

$0x1,-0x8(%rbp)

addl

int j = i - 3;

-0x8(%rbp),%eax

mov

$0x3,%eax

sub

%eax,-0x4(%rbp)

mov

i = i

-0x4(%rbp),%eax

MOV

%eax,-0x8(%rbp)

add

```

8 void bar() {

10

11

12

```

68 /* These are the core structs of the process record functionality.

69

70

A record_full_entry is a record of the value change of a register

("record_full_reg") or a part of memory ("record_full_mem"). And each

71

72

instruction must have a struct record_full_entry ("record_full_end")

73

that indicates that this is the last struct record_full_entry of this

74

instruction.

75

76

Each struct record_full_entry is linked to "record_full_list" by "prev"

and "next" pointers. */

141 struct record_full_entry

142 {

143

struct record_full_entry *prev;

144

struct record_full_entry *next;

145

enum record_full_type type;

146

union

147

148

/* reg */

149

struct record_full_reg_entry reg;

150

/* mem */

151

struct record_full_mem_entry mem;

/* end */

152

struct record_full_end_entry end;

gdb/record-full.c

153

154

} u;

155 };

```

→ /tmp gdb ./a.out

## Hofer et al. Design And Implementation of a Backward-In-Time Debugger

NODe '06

#### Design and Implementation of a Backward-In-Time Debugger\*

Christoph Hofer, Marcus Denker Software Composition Group University of Bern, Switzerland www.iam.unibe.ch/~scg

Stéphane Ducasse

LISTIC

Université de Savoie, France

www.listic.univ-savoie.fr

#### Abstract:

Traditional debugging and stepping execution trace are well-accepted techniques to understand deep internals about a program. However in many cases navigating the stack trace is not enough to find bugs, since the cause of a bug is often not in the stack trace anymore and old state is lost, so out of reach from the debugger. In this paper, we present the design and implementation of a backward-in-time debugger for a dynamic language, *i.e.*, a debugger that allows one to navigate back the history of the application. We present the design and implementation of a backward-in-time debugger called UNSTUCK and show our solution to key implementation challenges.

#### 1 Introduction

Debuggers offer the ability to stop a program at a chosen place, either due to an error or an explicit request (breakpoint). They provide the current states of the involved objects together with a stack trace. However, while stepping through the code is a powerful technique to get a deep understanding of a certain functionality [DDN02], in many cases this information is not enough to find bugs. The programmer is often forced to build new hypotheses about the possible cause of the bugs, set new breakpoints and restart the program to find the source of the problem. Often several iterations are necessary and it may be difficult to recreate the exact same context [LHS99].

The questions a programmer has are often: "where was this variable set?", "why is this object reference nil?" or "what was the previous state of that object?". A static debugger cannot answer these questions, since it has only access to the current execution stack. There is no possibility to backtrack the state of an object or to find out why especially this object was passed to a method. The Omniscient Debugger is a first attempt to answer these problems [Lew03], however it is limited to java and instrumentation is done at bytecode load time.

To understand the challenges faced by building a backward in time debugger, i.e., a debugger that allows one to query the state history of a program, we developed a backward

#### librip

Librip is a minimal-overhead API for instruction-level tracing in highly concurrent software. It is released under the Apache 2.0 license.

#### **Impetus**

Software with many thousands of threads and / or coroutines suffers from lack of run-time and post-mortem visibility with debugging tools. When many thousands of threads are present in a software system, it may be impossible to attach a debugger to an apparently stuck process. With many thousands of coroutines, even with a debugger, it can be difficult to even find a stuck coroutine on myriad scheduling lists -- especially if it is erroneously waiting for data in the kernel!

This library attempts to solve these problems through an API that is reasonably efficient in terms of both CPU and memory requirements -- enough so that traces can be take in production.

#### Design

As the name suggests, this library provides an interface for snapshots of the instruction pointer. These snapshots are stored in a per-thread ring buffer, and contain a packed counter / function address. (Additional interfaces allow registration for coroutines, but require additional runtime support.)

Currently, only Linux on amd64 architectures is supported. Patches for other platforms, operating systems, and compilers are more than welcome.

# Efficient timetraveling

Usenix '05

#### Debugging operating systems with time-traveling virtual machines

Samuel T. King, George W. Dunlap, and Peter M. Chen University of Michigan

#### Abstract

Operating systems are difficult to debug with traditional cyclic debugging. They are non-deterministic; they run for long periods of time; they interact directly with hardware devices; and their state is easily perturbed by the act of debugging. This paper describes a time-traveling virtual machine that overcomes many of the difficulties associated with debugging operating systems. Time travel enables a programmer to navigate backward and forward arbitrarily through the execution history of a particular run and to replay arbitrary segments of the past execution. We integrate time travel into a general-purpose debugger to enable a programmer to debug an OS in reverse, implementing commands such as reverse breakpoint, reverse watchpoint, and reverse single step. The space and time overheads needed to support time travel are reasonable for debugging, and movements in time are fast enough to support interactive debugging. We demonstrate the value of our time-traveling virtual machine by using it to understand and fix several OS bugs that are difficult to find with standard debugging tools. Reverse debugging is especially helpful in finding bugs that are fragile due to non-determinism, bugs in device drivers, bugs that require long runs to trigger, bugs that corrupt the stack, and bugs that are detected after the relevant stack frame is popped.

#### 1 Introduction

Computer programmers are all-too-familiar with the task of debugging complex software through a combination of detective work, guesswork, and systematic search. Tracking down a bug generally starts with running a program until an error in the program manifests as a fault. The programmer<sup>1</sup> then seeks to start from the fault (the manifestation of the error) and work backward to the cause of the fault (the programming error itself). Cyclic debugging is the classic way to work backward toward the error. In cyclic debugging, a programmer uses a debugger or output statements to examine the state of the program at a given point in its execution. Armed with

this information, the programmer then re-runs the program, stops it at an earlier point in its execution history, examines the state at this point, then iterates.

Unfortunately, this classic approach to debugging is difficult to apply when debugging operating systems. Many aspects of operating systems make them difficult to debug: they are non-deterministic; they run for long periods of time; the act of debugging may perturb their state; and they interact directly with hardware devices.

First, operating systems are non-deterministic. Their execution is affected by non-deterministic events such as the interleaving of multiple threads, interrupts, user input, network input, and the perturbations of state caused by the programmer who is debugging the system. This non-determinism makes cyclic debugging infeasible because the programmer cannot re-run the system to examine the state at an earlier point.

Second, operating systems run for long periods of time, such as weeks, months, or even years. Re-running the system in cyclic debugging would thus be infeasible even if the OS were completely deterministic.

Third, the act of debugging may perturb the state of the operating system. The converse is also true: a misbehaving operating system may corrupt the state of the debugger. These interactions are possible because the operating system is traditionally the lowest level of software on a computer, so the debugger's code and data is not isolated from the OS (unless the debugger uses specialized hardware such as an in-circuit emulator). Even remote kernel debuggers depend on some basic functionality in the debugged OS, such as reading and writing memory locations, setting and handling breakpoints, and communicating with the remote debugger (e.g., through the serial line). Using this basic functionality may be impossible on a sick OS. A debugger also needs assistance from the OS to access hardware devices, and this functionality may not work on a sick OS.

Finally, operating systems interact directly with hardware devices. Devices are sources of non-determinism that hinder cyclic debugging; they return data and generate interrupts that may change between runs. Devices may also fail due to timing dependencies if a programmer pauses during a debugging session.

In this paper, we describe how to use time-traveling virtual machines to overcome many of the difficulties as"...operating systems run for long periods of time, such as weeks, months, or even years."

<sup>&</sup>lt;sup>1</sup>In this paper, "programmer" refers to the person debugging the system, and "debugger" refers to the programming tool (e.g., 9db) used by the programmer to examine and control the program.

Usenix '05

#### Debugging operating systems with time-traveling virtual machines

Samuel T. King, George W. Dunlap, and Peter M. Chen University of Michigan

#### Abstract

Operating systems are difficult to debug with traditional cyclic debugging. They are non-deterministic; they run for long periods of time; they interact directly with hardware devices; and their state is easily perturbed by the act of debugging. This paper describes a time-traveling virtual machine that overcomes many of the difficulties associated with debugging operating systems. Time travel enables a programmer to navigate backward and forward arbitrarily through the execution history of a particular run and to replay arbitrary segments of the past execution. We integrate time travel into a general-purpose debugger to enable a programmer to debug an OS in reverse, implementing commands such as reverse breakpoint, reverse watchpoint, and reverse single step. The space and time overheads needed to support time travel are reasonable for debugging, and movements in time are fast enough to support interactive debugging. We demonstrate the value of our time-traveling virtual machine by using it to understand and fix several OS bugs that are difficult to find with standard debugging tools. Reverse debugging is especially helpful in finding bugs that are fragile due to non-determinism, bugs in device drivers, bugs that require long runs to trigger, bugs that corrupt the stack, and bugs that are detected after the relevant stack frame is popped.

#### 1 Introduction

Computer programmers are all-too-familiar with the task of debugging complex software through a combination of detective work, guesswork, and systematic search. Tracking down a bug generally starts with running a program until an error in the program manifests as a fault. The programmer<sup>1</sup> then seeks to start from the fault (the manifestation of the error) and work backward to the cause of the fault (the programming error itself). Cyclic debugging is the classic way to work backward toward the error. In cyclic debugging, a programmer uses a debugger or output statements to examine the state of the program at a given point in its execution. Armed with

this information, the programmer then re-runs the program, stops it at an earlier point in its execution history, examines the state at this point, then iterates.

Unfortunately, this classic approach to debugging is difficult to apply when debugging operating systems. Many aspects of operating systems make them difficult to debug: they are non-deterministic; they run for long periods of time; the act of debugging may perturb their state; and they interact directly with hardware devices.

First, operating systems are non-deterministic. Their execution is affected by non-deterministic events such as the interleaving of multiple threads, interrupts, user input, network input, and the perturbations of state caused by the programmer who is debugging the system. This non-determinism makes cyclic debugging infeasible because the programmer cannot re-run the system to examine the state at an earlier point.

Second, operating systems run for long periods of time, such as weeks, months, or even years. Re-running the system in cyclic debugging would thus be infeasible even if the OS were completely deterministic.

Third, the act of debugging may perturb the state of the operating system. The converse is also true: a misbehaving operating system may corrupt the state of the debugger. These interactions are possible because the operating system is traditionally the lowest level of software on a computer, so the debugger's code and data is not isolated from the OS (unless the debugger uses specialized hardware such as an in-circuit emulator). Even remote kernel debuggers depend on some basic functionality in the debugged OS, such as reading and writing memory locations, setting and handling breakpoints, and communicating with the remote debugger (e.g., through the serial line). Using this basic functionality may be impossible on a sick OS. A debugger also needs assistance from the OS to access hardware devices, and this functionality may not work on a sick OS.

Finally, operating systems interact directly with hardware devices. Devices are sources of non-determinism that hinder cyclic debugging; they return data and generate interrupts that may change between runs. Devices may also fail due to timing dependencies if a programmer pauses during a debugging session.

In this paper, we describe how to use time-traveling virtual machines to overcome many of the difficulties as-

<sup>&</sup>lt;sup>1</sup>In this paper, "programmer" refers to the person debugging the system, and "debugger" refers to the programming tool (e.g., 9db) used by the programmer to examine and control the program.

Usenix '05

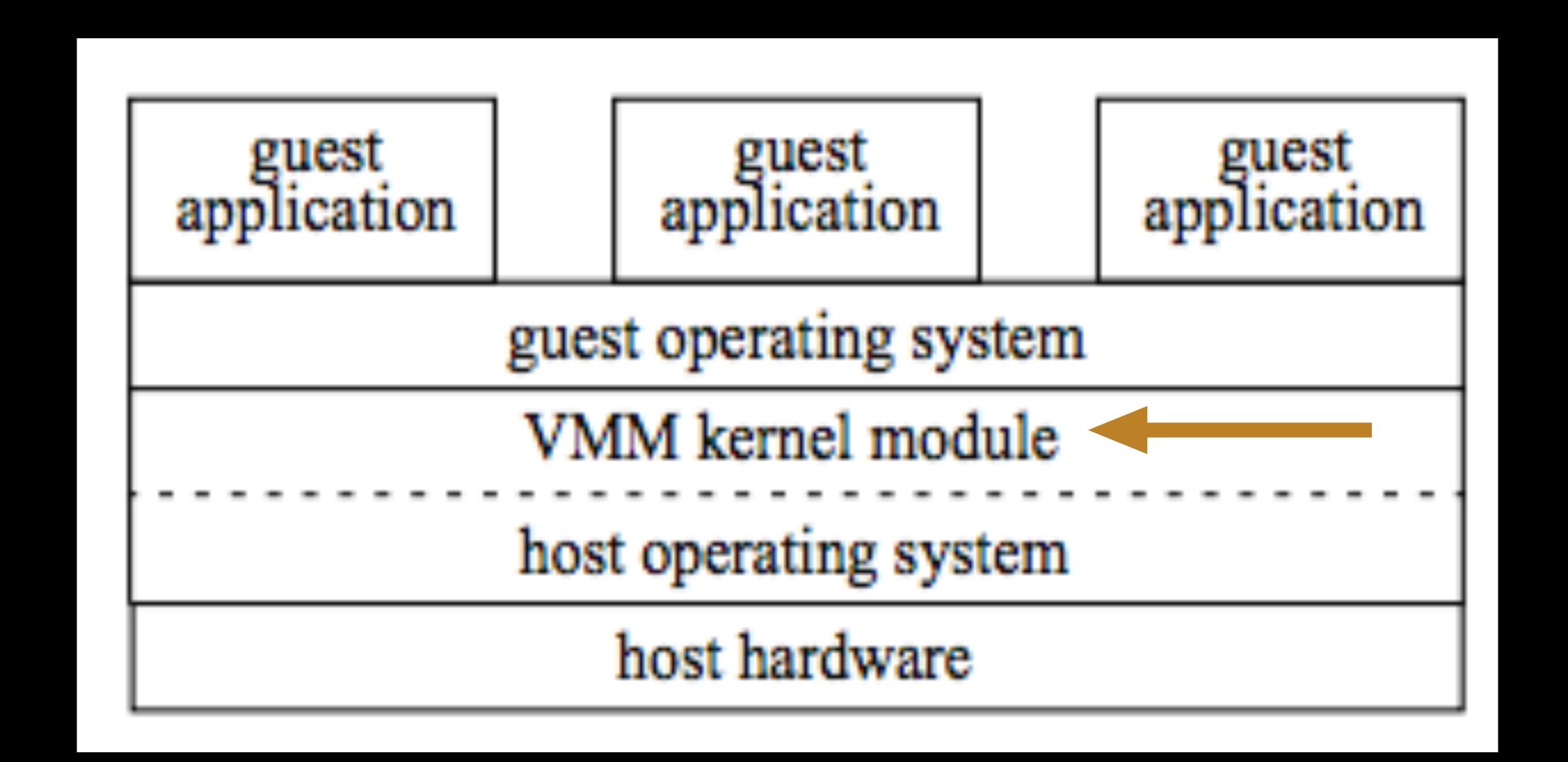

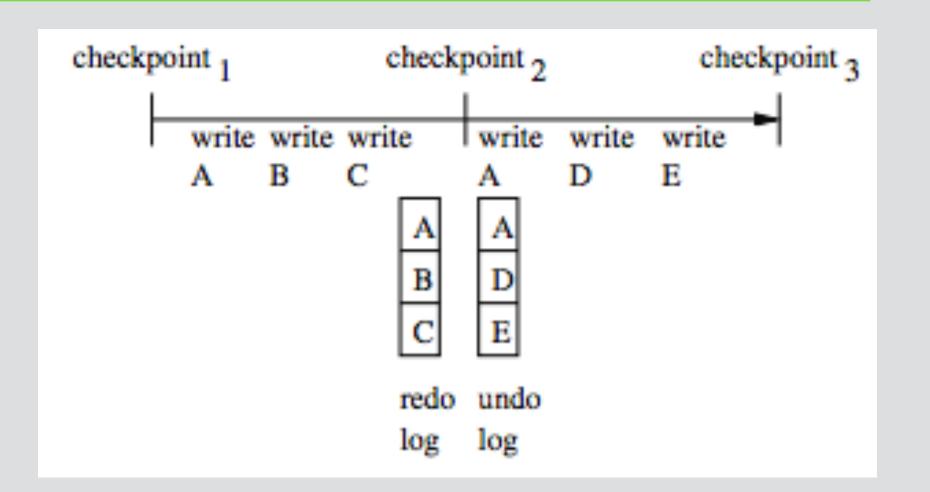

#### 3 Time-traveling virtual machines

A time-traveling virtual machine should have two capabilities. First, it should be able to reconstruct the complete state of the virtual machine at any point in a run, where a run is defined as the time from when the virtual machine was powered on to the last instruction it executed. Second, it should be able to start from any point in a run and from that point replay the same instruction stream that was executed during the original run from that point. This section describes how TTVM achieves these capabilities through a combination of logging, replay, and checkpointing.

#### 3.1 Logging and replaying a VM

The foundational capability in TTVM is the ability to replay a run from a given point in a way that matches the original run instruction for instruction. Replay causes the virtual machine to transition through the same states as it went through during the original run; hence replay enables one to reconstruct the complete state of the virtual machine at any point in the run. TTVM uses the ReVirt logging/replay system to provide this capability [9]. This section briefly summarizes how ReVirt logs and replays the execution of a virtual machine.

A virtual machine can be replayed by starting from a checkpoint, then replaying all sources of non-determinism [5, 9]. For UML, the sources of non-determinism are external input from the network, key-board, and real-time clock and the timing of virtual interrupts. The VMM replays network and keyboard input by logging the calls that read these devices during the original run and regenerating the same data during the replay run. Likewise, we configure the CPU to cause reads of the real-time clock to trap to the VMM, where they can be logged or regenerated.

To replay a virtual interrupt, ReVirt logs the instruction in the run at which it was delivered and re-delivers the interrupt at this instruction during replay. This point is identified uniquely by the number of branches since the start of the run and the address of the interrupted instruction [19]. ReVirt uses a performance counter on the Intel Pentium 4 CPU to count the number of branches during logging, and it uses the same performance counter and instruction breakpoints to stop at the interrupted instruction during replay. Replaying interrupts enables ReVirt to replay the scheduling order of multi-threaded guest operating systems and applications, as long as the VMM exports the abstraction of a uniprocessor virtual machine [22]. Researchers are investigating ways to support replay on multiprocessors [29].

#### 3.2 Host device drivers in the guest OS

In general, VMMs export a limited set of virtual devices. Some VMMs export virtual devices that exist in hardware (e.g., VMware Workstation exports an emulated AMD Lance Ethernet card); others (like UML) export virtual devices that have no hardware equivalent. Exporting a limited set of virtual devices to the guest OS is usually considered a benefit of virtual-machine systems, because it frees guest OSs from needing device drivers for myriad host devices [26]. However, when using virtual machines to debug operating systems, the limited set of virtual devices prevents programmers from using and debugging drivers for real devices; programmers can only debug the architecture-independent portion of the guest OS. There are two ways to address this limitation and enable the programmer to run and debug real device drivers in a guest OS. With both strategies, real device drivers can be included in the guest OS without being modified

The first way to run a real device driver in the guest OS is for the VMM to provide a software emulator for that device. The device driver issues the normal set of I/O instructions: IN/OUT instructions, memory-mapped I/O, DMA commands, and interrupts. The VMM traps these privileged instructions and forwards them to/from the software device emulator. With this strategy, ReVirt can log and replay device driver code in the same way it logs and replays the rest of the guest OS. If one runs the VMM's software device emulator above ReVirt's logging system (and above the checkpoint system described in Section 3.3), ReVirt will guide the emulator and device driver code through the same instruction sequence during replay as they executed during logging. While this first strategy fits in well with the existing ReVirt system, it only works if one has an accurate software emulator for the device whose driver one wishes to debug.

We modified UML to provide a second way to run real device drivers in the guest OS, which works even when no software emulator exists for the device of interest. With this strategy, the VMM traps and forwards the privileged I/O instructions and DMA requests issued by the guest OS device driver to the actual hardware. The programmer specifies which devices UML can access, and the VMM enforces the proper I/O port space and memory access for the device.

This second strategy requires extensions to enable Re-Virt to log and replay the execution of the device driver. Whereas the first strategy placed the device emulator above the ReVirt logging layer, the second strategy forwards driver actions to the actual hardware device. Because this device may not be deterministic, ReVirt must log any information sent from the device to the driver. Specifically, ReVirt must log and replay the data returned "Replay causes the virtual machine to transition through the same states as it went through during the original run"

"A VM can be replayed by starting from a checkpoint, then replaying [...] the network, keyboard, clock, and timing of interrupts"

## Peterministic Replay

Usenix '05

6]. User-Mode Linux simulates interrupts and preemptions with asynchronous signals, and prior reverse debuggers are not able to replay such events. In addition, most reverse debuggers implement time travel by logging all changes to variables [30, 1, 21, 6], and this approach logs too much data when debugging long-running systems such as an OS. Finally, some systems work at the language level [27], and this prevents them from working with operating systems in a different language or with application binaries.

Researchers have worked to replay non-deterministic programs through various approaches. The events of different threads can be replayed at different levels, including logging accesses to shared objects [16], logging the scheduling order of multi-threaded programs on a uniprocessor [22], or logging physical memory accesses in hardware [2]. Other researchers have worked to optimize the amount of data logged [21].

Virtual-machine replay has been used for nondebugging purposes. Hypervisor used virtual-machine replay to synchronize the state of a backup machine to provide fault tolerance [5]. ReVirt used virtual-machine replay to enable detailed intrusion analysis [9]. Our work applies virtual-machine replay to achieve a new capability, which is reverse debugging of operating systems. TTVM also supports additional features over prior virtual-machine replay systems. TTVM supports the ability to run, log, and replay real device drivers in the guest OS, whereas prior virtual-machine replay systems ran only para-virtualized device drivers in the guest OS. In addition, TTVM can travel quickly forward and backward in time through its use of checkpoints and undo and redo logs, whereas ReVirt supported only a single checkpoint of a powered-off virtual machine and Hypervisor did not need to support time travel at all (it only supported replay within an epoch).

Another approach for providing time travel is to use a complete machine simulator, such as Simics [18]. Simics supports deterministic replay for operating systems and applications and has an interface to a debugger. However, Simics is drastically slower than TTVM, and this makes debugging long runs impractical. On a 750 MHz Ultraspare III, Simics executes 2-6 million x86 instructions per second (several hundred times slower than native) [18], whereas virtual machines typically incur a slowdown of less than 2x.

#### 8 Conclusions and future work

We have described the design and implementation of a time-traveling virtual machine and shown how to use TTVM to add powerful capabilities for debugging operating systems. We integrated TTVM with a generalpurpose debugger, implementing commands such as reverse breakpoint, reverse watchpoint, and reverse step.

TTVM added reasonable overhead in the context of debugging. The logging needed to support time travel for three OS-intensive workloads added 3-12% in running time and 2-85 KB/sec in log space. Taking checkpoints every minute added less than 4% time overhead and 1-5 MB/sec space overhead. Taking checkpoints every 10 second to prepare for debugging a portion of a run added 16-33% overhead and enabled reverse debugging commands to complete in about 12 seconds.

We used TTVM and our new reverse debugging commands to fix four OS bugs that were difficult to find with standard debugging tools. We found the reverse debugging commands to be intuitive to understand and fast and easy to use. Reverse debugging proved especially helpful in finding bugs that were fragile due to non-determinism, bugs in device drivers, bugs that required long runs to trigger, bugs that corrupted the stack, and bugs that were detected after the relevant stack frame was popped.

Possible future work includes exploring nontraditional debugging operations that are enabled by time travel and deterministic replay. For example, one could measure the effects of a programmer-induced change by forking the execution and comparing the results after the change with the results of the original

#### 9 Acknowledgments

Our shepherd, Steve Gribble, and the anonymous reviews provided feedback that helped improve this paper. This research was supported in part by ARDA grant NBCHC030104, National Science Foundation grants CCR-0098229 and CCR-0219085, and by Intel Corporation. Samuel King was supported in part by a National Defense Science and Engineering Graduate Fellowship.

#### References

- H. Agrawal, R. A. DeMillo, and E. H. Spafford. An Execution-Backtracking Approach to Debugging. *IEEE Software*, 8(3), May 1991.

- [2] D. F. Bacon and S. C. Goldstein. Hardware-Assisted Replay of Multiprocessor Programs. In Proceedings of the ACM/ONR Workshop on Parallel and Distributed Debugging, May 1991.

- [3] P. Barham, B. Dragovic, K. Fraser, S. Hand, T. Harris, A. Ho, R. Neugebauer, I. Pratt, and A. Warfield. Xen and the Art of Virtualization. In Proceedings of the 2003 Symposium on Operating Systems Principles, October 2003.

- [4] B. Boothe. Efficient algorithms for bidirectional debugging. In Proceedings of the 2000 Conference on Programming Language Design and Implementation (PLDI), pages 299–310, June 2000.

"The logging added 3-12% in running time and 2-85 KB/sec in log space."

"Taking checkpoints every minute added less than 4% time overhead and 1-5 MB/sec space overhead."

"Taking checkpoints every 10 second added 16-33% overhead and enabled reverse debugging commands to complete in about 12 seconds"

- GDB: linked list storage of every memory op

- + Easy to build and reason about

- Both recording and replaying is very slow

- King (et al): Periodic state checkpointing

- + Easy to jump between large period of time

- + Can trade better fidelity for greater overhead

- Have to replay execution between checkpoints

- King (et al): Only records external, non-deterministic events

- + Reduces log size and improves performance

- synchronizing external events becomes complicated

# Improving performance with IIT compilation

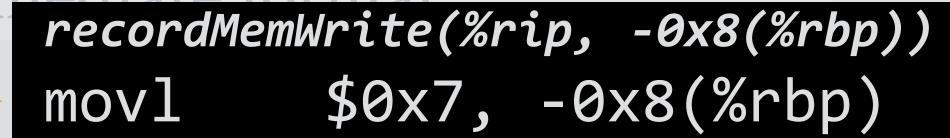

## compilation-based tooling

- Rather than interrupt execution to return control-flow to a debugger, weave instrumentation into the existing codebase at runtime

- Allows for both better performance and more flexible analysis tools

## Luk et al. Pin: Building Customized Program Analysis Tools w/ Dynamic Instrumentation

PLDI '05

#### Pin: Building Customized Program Analysis Tools with Dynamic Instrumentation

Chi-Keung Luk Robert Cohn Robert Muth Harish Patil Artur Klauser Geoff Lowney Steven Wallace Vijay Janapa Reddi † Kim Hazelwood

Intel Corporation †University of Colorado

Website: http://rogue.colorado.edu/Pin, Email: pin.project@intel.com

#### Abstract

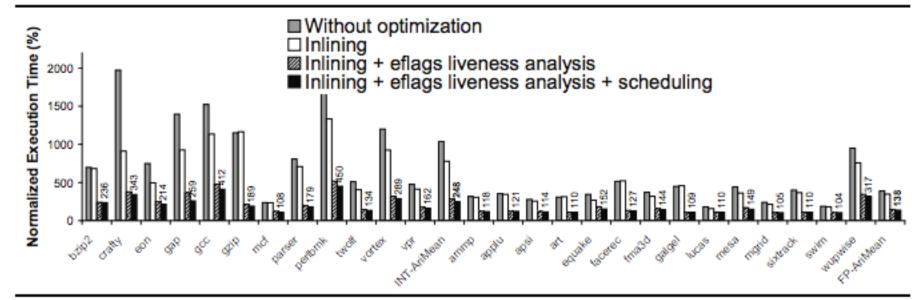

Robust and powerful software instrumentation tools are essential for program analysis tasks such as profiling, performance evaluation, and bug detection. To meet this need, we have developed a new instrumentation system called Pin. Our goals are to provide easy-to-use, portable, transparent, and efficient instrumentation. Instrumentation tools (called Pintools) are written in C/C++ using Pin's rich API. Pin follows the model of ATOM, allowing the tool writer to analyze an application at the instruction level without the need for detailed knowledge of the underlying instruction set. The API is designed to be architecture independent whenever possible, making Pintools source compatible across different architectures. However, a Pintool can access architecture-specific details when necessary. Instrumentation with Pin is mostly transparent as the application and Pintool observe the application's original, uninstrumented behavior. Pin uses dynamic compilation to instrument executables while they are running. For efficiency, Pin uses several techniques, including inlining, register re-allocation, liveness analysis, and instruction scheduling to optimize instrumentation. This fully automated approach delivers significantly better instrumentation performance than similar tools. For example, Pin is 3.3x faster than Valgrind and 2x faster than DynamoRIO for basic-block counting. To illustrate Pin's versatility, we describe two Pintools in daily use to analyze production software. Pin is publicly available for Linux platforms on four architectures: IA32 (32-bit x86), EM64T (64-bit x86), Itanium®, and ARM. In the ten months since Pin 2 was released in July 2004, there have been over 3000 downloads from its website.

Categories and Subject Descriptors D.2.5 [Software Engineering]: Testing and Debugging-code inspections and walk-throughs, debugging aids, tracing; D.3.4 [Programming Languages]: Processorscompilers, incremental compilers

General Terms Languages, Performance, Experimentation

Keywords Instrumentation, program analysis tools, dynamic compilation

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

PLDI'05 June 12-15,2005, Chicago, Illinois, USA. Copyright © 2005 ACM 1-59593-080-9/05/0006 . . . \$5.00.

#### 1. Introduction

As software complexity increases, instrumentation—a technique for inserting extra code into an application to observe its behavior is becoming more important. Instrumentation can be performed at various stages: in the source code, at compile time, post link time, or at run time. Pin is a software system that performs run-time binary instrumentation of Linux applications.

The goal of Pin is to provide an instrumentation platform for building a wide variety of program analysis tools for multiple architectures. As a result, the design emphasizes ease-of-use, portability, transparency, efficiency, and robustness. This paper describes the design of Pin and shows how it provides these features.

Pin's instrumentation is easy to use. Its user model is similar to the popular ATOM [30] API, which allows a tool to insert calls to instrumentation at arbitrary locations in the executable. Users do not need to manually inline instructions or save and restore state. Pin provides a rich API that abstracts away the underlying instruction set idiosyncrasies, making it possible to write portable instrumentation tools. The Pin distribution includes many sample architecture-independent Pintools including profilers, cache simulators, trace analyzers, and memory bug checkers. The API also allows access to architecture-specific information.

Pin provides efficient instrumentation by using a just-in-time (JIT) compiler to insert and optimize code. In addition to some standard techniques for dynamic instrumentation systems including code caching and trace linking, Pin implements register reallocation, inlining, liveness analysis, and instruction scheduling to optimize jitted code. This fully automated approach distinguishes Pin from most other instrumentation tools which require the user's assistance to boost performance. For example, Valgrind [22] relies on the tool writer to insert special operations in their intermediate representation in order to perform inlining; similarly DynamoRIO [6] requires the tool writer to manually inline and save/restore application registers.

Another feature that makes Pin efficient is process attaching and detaching. Like a debugger, Pin can attach to a process, instrument it, collect profiles, and eventually detach. The application only incurs instrumentation overhead during the period that Pin is attached. The ability to attach and detach is a necessity for the instrumentation of large, long-running applications.

Pin's JIT-based instrumentation defers code discovery until run time, allowing Pin to be more robust than systems that use static instrumentation or code patching. Pin can seamlessly handle mixed code and data, variable-length instructions, statically unknown indirect jump targets, dynamically loaded libraries, and dynamically generated code.

Pin preserves the original application behavior by providing instrumentation transparency. The application observes the same ad"The goal is to provide an implementation platform for building program analysis tools"

"Its API allows a tool to insert calls to instrumentation at arbitrary locations in the executable"

"Pin provides efficient instrumentation by using a just-in-time compiler to insert and optimize code"

dresses (both instruction and data) and same values (both register

- 4 byte write to 0x7fff572b3b1c

- 4 byte write to 0x7fff572b3b1c

- 1 byte write to 0x7f86c0c04b00

- 1 byte write to 0x7f86c0c04b04

- 4 byte write to 0x7fff572b3b20

### Luk et al. Pin: Building Customized Program Analysis Tools w/ Dynamic Instrumentation

PLDI '05

### Pin: Building Customized Program Analysis Tools with Dynamic Instrumentation

Chi-Keung Luk

recordMemWrite(%rip,

Website: http://rogue.colorado.edu/Pin, Email: pin.project@intel.com

recordMemWrite(%rip,

### Abstract

Robust and powerful software instrume for program analysis tasks such as prot ation, and bug detection. To meet this a new instrumentation system called P vide easy-to-use, portable, transparent, tion. Instrumentation tools (called Pinto using Pin's rich API. Pin follows the model of ATOM, allowing the tool writer to analyze an application at out the need for detailed knowledge of set. The API is designed to be architector possible, making Pintools source compat tectures. However, a Pintool can access a

when necessary. Instrumentation with Pin is mostly transparent as

the application and Pintool observe the application's original, uninstrumented behavior. Pin uses dynamic compilation to instrument

executables while they are running. For efficiency, Pin uses several techniques, including inlining, register re-allocation, liveness

analysis, and instruction scheduling to optimize instrumentation.

This fully automated approach delivers significantly better instrumentation performance than similar tools. For example, Pin is 3.3x

faster than Valgrind and 2x faster than DynamoRIO for basic-block

counting. To illustrate Pin's versatility, we describe two Pintools

in daily use to analyze production software. Pin is publicly available for Linux platforms on four architectures: IA32 (32-bit x86),

EM64T (64-bit x86), Itanium®, and ARM. In the ten months since

Pin 2 was released in July 2004, there have been over 3000 downloads from its website.

Categories and Subject Descriptors D.2.5 [Software Engineering]: Testing and Debugging-code inspections and walk-throughs, debugging aids, tracing; D.3.4 [Programming Languages]: Processorscompilers, incremental compilers

General Terms Languages, Performance, Experimentation

Keywords Instrumentation, program analysis tools, dynamic compilation

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

PLDF'05 June 12–15,2005, Chicago, Illinois, USA. Copyright © 2005 ACM 1-59593-080-9/05/0006 . . . \$5.00. to the popular ATOM [30] API, which allows a tool to insert calls to instrumentation at arbitrary locations in the executable. Users do not need to manually inline instructions or save and restore state. Pin provides a rich API that abstracts away the underlying instruction set idiosyncrasies, making it possible to write portable instrumentation tools. The Pin distribution includes many sample architecture-independent Pintools including profilers, cache simulators, trace analyzers, and memory bug checkers. The API also allows access to architecture-specific information.

Pin provides efficient instrumentation by using a just-in-time (JIT) compiler to insert and optimize code. In addition to some standard techniques for dynamic instrumentation systems including code caching and trace linking, Pin implements register reallocation, inlining, liveness analysis, and instruction scheduling to optimize jitted code. This fully automated approach distinguishes Pin from most other instrumentation tools which require the user's assistance to boost performance. For example, Valgrind [22] relies on the tool writer to insert special operations in their intermediate representation in order to perform inlining; similarly DynamoRIO [6] requires the tool writer to manually inline and save/restore application registers.

Another feature that makes Pin efficient is process attaching and detaching. Like a debugger, Pin can attach to a process, instrument it, collect profiles, and eventually detach. The application only incurs instrumentation overhead during the period that Pin is attached. The ability to attach and detach is a necessity for the instrumentation of large, long-running applications.

Pin's JIT-based instrumentation defers code discovery until run time, allowing Pin to be more *robust* than systems that use static instrumentation or code patching. Pin can seamlessly handle mixed code and data, variable-length instructions, statically unknown indirect jump targets, dynamically loaded libraries, and dynamically generated code.

Pin preserves the original application behavior by providing instrumentation transparency. The application observes the same ad-

dresses (both instruction and data) and same values (both register

8 void bar() {

&i); int i = 7;

&i); i++;

&j); int j = i - 3;

&i): i - i + i

TRACE AddInstrumentFunction()

RTN AddInstrumentFunction()

IMG\_AddInstrumentFunction()

```

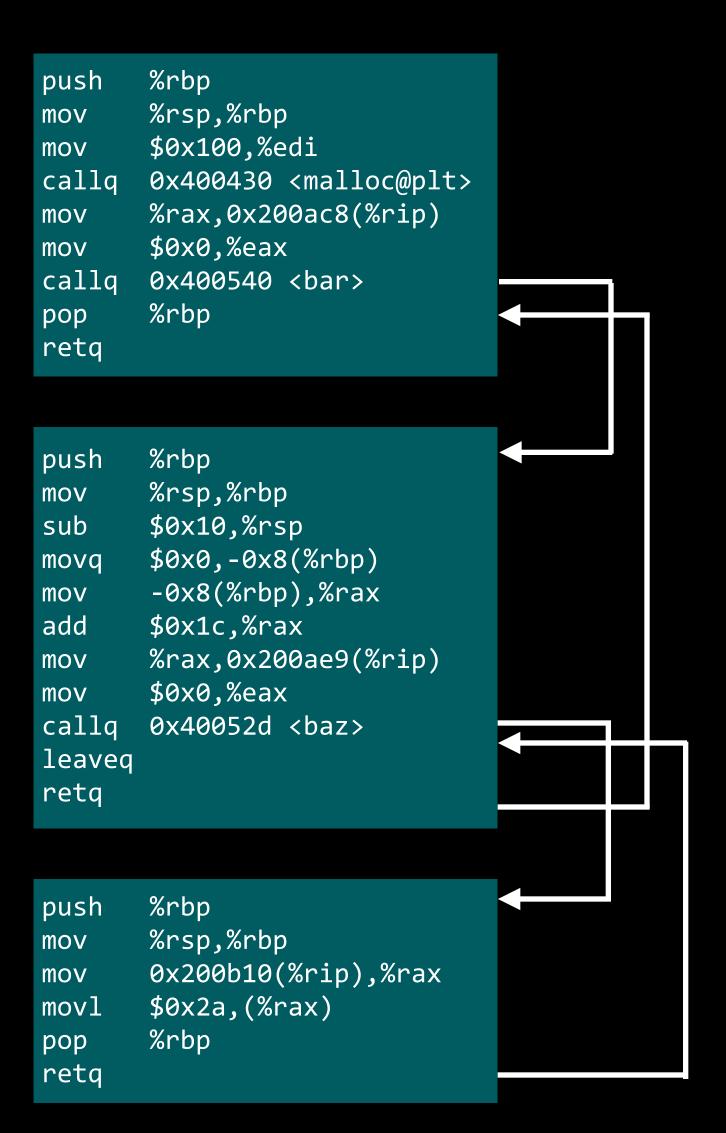

push %rbp

mov %rsp,%rbp

mov $0x100,%edi

callq 0x400430 <malloc@plt>

```

```

push %rbp

mov %rsp,%rbp

mov $0x100,%edi

callq 0x400430 <malloc@plt>

mov %rax,0x200ac8(%rip)

mov $0x0,%eax

callq 0x400540 <bar>

pop %rbp

retq

```

```

push

%rbp

%rsp,%rbp

% mov

push

% sub

mov

%rbp

push

movq

mov

%rsp,%rbp

callq

0: mov

0x200b10(%rip),%rax

mov

$0x2a,(%rax)

\frac{1}{2} mov 1

$ mov

mov

%rbp

pop

callq

0: mov

retq

% callq

pop

leaveq

retq

retq

```

```

static void

if (tcode == COMPONENT REF) {

instrument_gimple (gimple_stmt_iterator gsi)

tree field = TREE_OPERAND (expr, 1);

if (TREE_CODE (field) == FIELD_DECL) {

unsigned i;

fld_off = TREE_INT_CST_LOW (DECL_FIELD_BIT_OFFSET (field));

gimple stmt;

fld size = TREE INT CST LOW (DECL SIZE (field));

enum gimple_code gcode;

if (((fld off % BITS PER UNIT) != 0)

tree rhs, lhs;

|| ((fld_size % BITS_PER_UNIT) != 0)) {

/* As of now it crashes compilation.

stmt = gsi_stmt (gsi);

TODO: handle bit-fields as if touching the whate field. */ gcc_assert (is_gimple_addressable (expr));

gcode = gimple_code (stmt);

return;

if (gcode == GIMPLE_ASSIGN) {

/* Handle assignment lhs as store. */

lhs = gimple assign lhs (stmt);

instrument_expr (gsi, lhs, 1);

/* Handle operands as loads. */

/* TODO: handle other cases

for (i = 1; i < gimple_num_ops (stmt); i++) {

(FIELD_DECL, MEM_REF, ARRAY_RANGE_REF, TARGET_MEM_REF, ADDR_EXPR). */

rhs = gimple_op (stmt, i);

if (tcode != ARRAY_REF

instrument_expr (gsi, rhs, 0);

&& tcode != VAR_DECL && tcode != COMP_NENT_REF

&& tcode != INDIRECT_REF && tcode / MEM_REF)

return;

func mops++;

stmt = gsi_stmt (gsi);

static void

loc = gimple_location (stmt)

instrument_expr (gimple_stmt_iterator gsi, tree expr, int is_write)

rhs = is vptr store (stmt expr, is write);

if (rhs == NULL)

enum tree_code tcode;

gs = instr_memory_access (expr, is_write);

unsigned fld_off, fld_size;

else

tree base, rhs;

gs = instr_vptr_update (expr, rhs);

gimple stmt;

set_location (gs, loc);

gimple_seq gs;

/* Instrumentation for assignment of a function result

location_t loc;

must be inserted after the call. Instrumentation for

reads of function arguments must be inserted before the call.

base = get_base_address (expr);

That's because the call can contain synchronization. */

if (base == NULL_TREE | TREE_CODE (base) == SSA_NAME

if (is_gimple_call (stmt) && is_write)

|| TREE CODE (base) == STRING CST)

gsi_insert_seq_after (&gsi, gs, GSI_NEW_STMT);

return;

else

gsi_insert_seq_before (&gsi, gs, GSI_SAME_STMT);

tcode = TREE_CODE (expr);

/* Below are things we do not instrument

(no possibility of races or not implemented yet). */

if (/* Compiler-emitted artificial variables. */

(DECL P (expr) && DECL ARTIFICIAL (expr))

/* The var does not live in memory -> no possibility of races. */

(tcode == VAR_DECL

&& TREE_ADDRESSABLE (expr) == 0

&& TREE STATIC (expr) == 0)

^{\prime *} Not implemented. ^{*}/

TREE_CODE (TREE_TYPE (expr)) == RECORD_TYPE

tcode == CONSTRUCTOR

tcode == PARM DECL

/* Load of a const variable/parameter/field. */

| is_load_of_const (expr, is_write))

return;

```

```

static gimple seq

instr_memory_access (tree expr, int is_write)

tree addr_expr, expr_type, call_expr, fdecl;

gimple_seq gs;

unsigned size;

addr_expr = build_addr (unshare_expr (expr), current_function_decl);

expr_type = TREE_TYPE (expr);

while (TREE_CODE (expr_type) == ARRAY_TYPE)

expr_type = TREE_TYPE (expr_type);

size = (TREE_INT_CST_LOW (TYPE_SIZE (expr_type))) / BITS_PER_UNIT;

fdecl = get_memory_access_decl (is_write, size);

call_expr = build_call_expr (fdecl, 1, addr_expr);

gs = NULL;

force_gimple_operang (call_expr, &gs, true, 0);

return gs;

static tree

get memory access decl (int is write, unsigned size)

tree typ, *decl;

char fname [64];

static tree cache [2][17];

is_write = !!is_write;

if (size <= 1)

size = 1;

else if (size <= 3)

size = 2;

else if (size <= 7)

size = 4;

else if (size <= 15)

size = 8;

else

size = 16;

decl = &cache[is_write][size];

if (*decl == NULL) {

snprintf(fname, sizeof fname, "__tsan_%s%d",

is_write ? "write" : "read", size);

typ = build_function_type_list (void_type_node,

ptr type node, NULL TREE);

*decl = build_func_decl (typ, fname);

return *decl;

```

# Luk et al. Pin: Building Customized Program Analysis Tools w/ Dynamic Instrumentation

PLDI '05

Although EM64T is a 64-bit extension of IA32, we classify it as a separate architecture because of its many new features such as 64-bit addressing, a flat address space, twice the number of registers, and new software conventions [15].

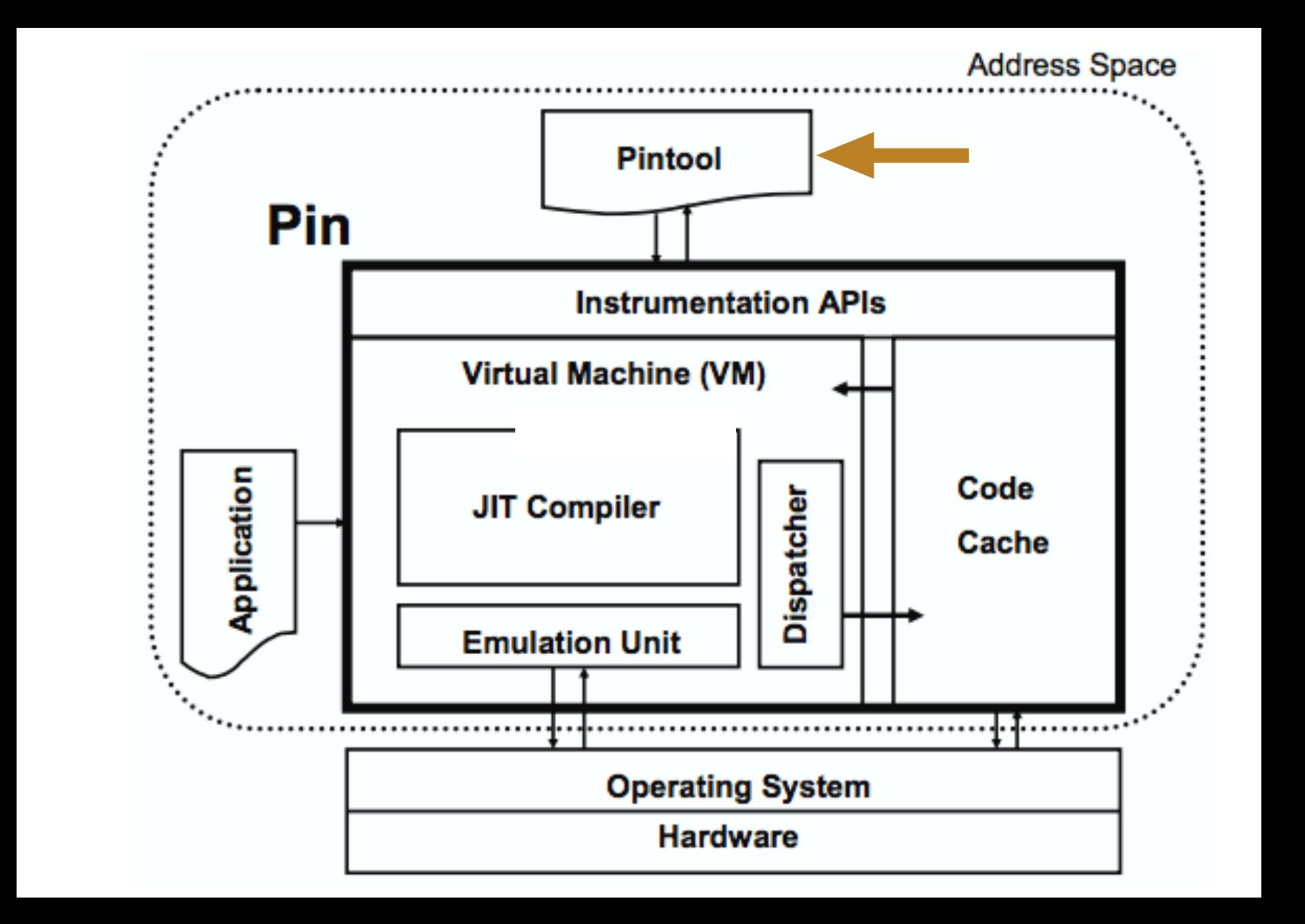

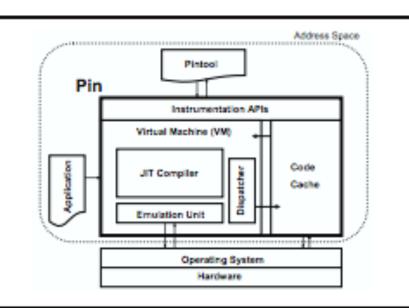

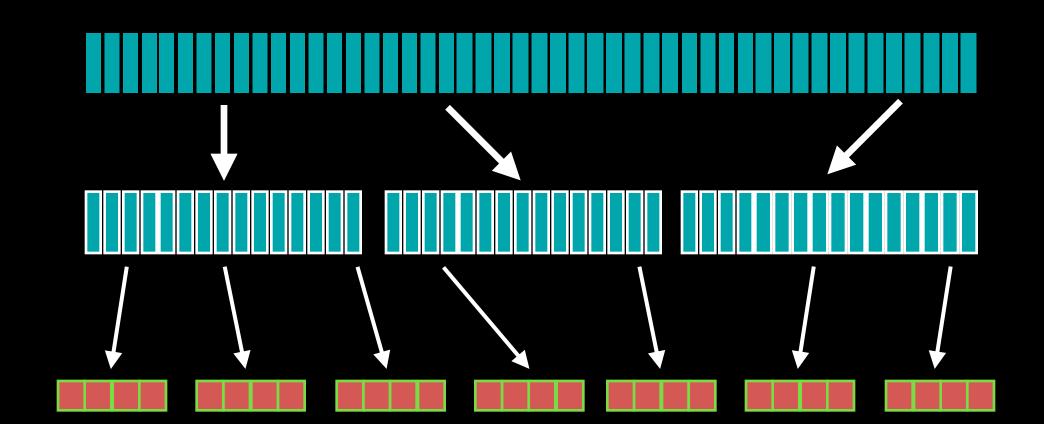

Figure 2. Pin's software architecture

mentation API invoked by Pintools. The VM consists of a just-intime compiler (JIT), an emulator, and a dispatcher. After Pin gains

control of the application, the VM coordinates its components to

execute the application. The JIT compiles and instruments application code, which is then launched by the dispatcher. The compiled

code is stored in the code cache. Entering/leaving the VM from/to

the code cache involves saving and restoring the application register

state. The emulator interprets instructions that cannot be executed

directly. It is used for system calls which require special handling

from the VM. Since Pin sits above the operating system, it can only

capture user-level code.

As Figure 2 shows, there are three binary programs present when an instrumented program is running: the application, Pin, and the Pintool. Pin is the engine that jits and instruments the application. The Pintool contains the instrumentation and analysis routines and is linked with a library that allows it to communicate with Pin. While they share the same address space, they do not share any libraries and so there are typically three copies of glibc. By making all of the libraries private, we avoid unwanted interaction between Pin, the Pintool, and the application. One example of a problematic interaction is when the application executes a glibc function that is not reentrant. If the application starts executing the function and then tries to execute some code that triggers further compilation, it will enter the JIT. If the JIT executes the same glibc function, it will enter the same procedure a second time while the application is still executing it, causing an error. Since we have separate copies of glibe for each component, Pin and the application do not share any data and cannot have a re-entrancy problem. The same problem can occur when we jit the analysis code in the Pintool that calls glibc (jitting the analysis routine allows us to greatly reduce the overhead of simple instrumentation on Itanium).

### 3.2 Injecting Pin

The injector loads Pin into the address space of an application. Injection uses the Unix Ptrace API to obtain control of an application and capture the processor context. It loads the Pin binary into the application address space and starts it running. After initializing itself, Pin loads the Pintool into the address space and starts it running. The Pintool initializes itself and then requests that Pin start the application. Pin creates the initial context and starts jitting the application at the entry point (or at the current PC in the case of attach). Using Ptrace as the mechanism for injection allows us to attach to an already running process in the same way as a debugger. It is also possible to detach from an instrumented process and continue executing the original, uninstrumented code.

### 3.1 System Overview

Figure 2 illustrates Pin's software architecture. At the highest level, Pin consists of a virtual machine (VM), a code cache, and an instru-

Other tools like DynamoRIO [6] rely on the LD\_PRELOAD environment variable to force the dynamic loader to load a shared

library in the address space. First, LD\_PRELOAD does not work with

statically-linked binaries, which many of our users require. Second, loading an extra shared library will shift all of the application shared libraries and some dynamically allocated memory to

a higher address when compared to an uninstrumented execution.

We attempt to preserve the original behavior as much as possible.

Third, the instrumentation tool cannot gain control of the application until after the shared-library loader has partially executed,

while our method is able to instrument the very first instruction in

the program. This capability actually exposed a bug in the Linux

shared-library loader, resulting from a reference to uninitialized

data on the stack.

### 3.3 The JIT Compiler

### 3.3.1 Basics

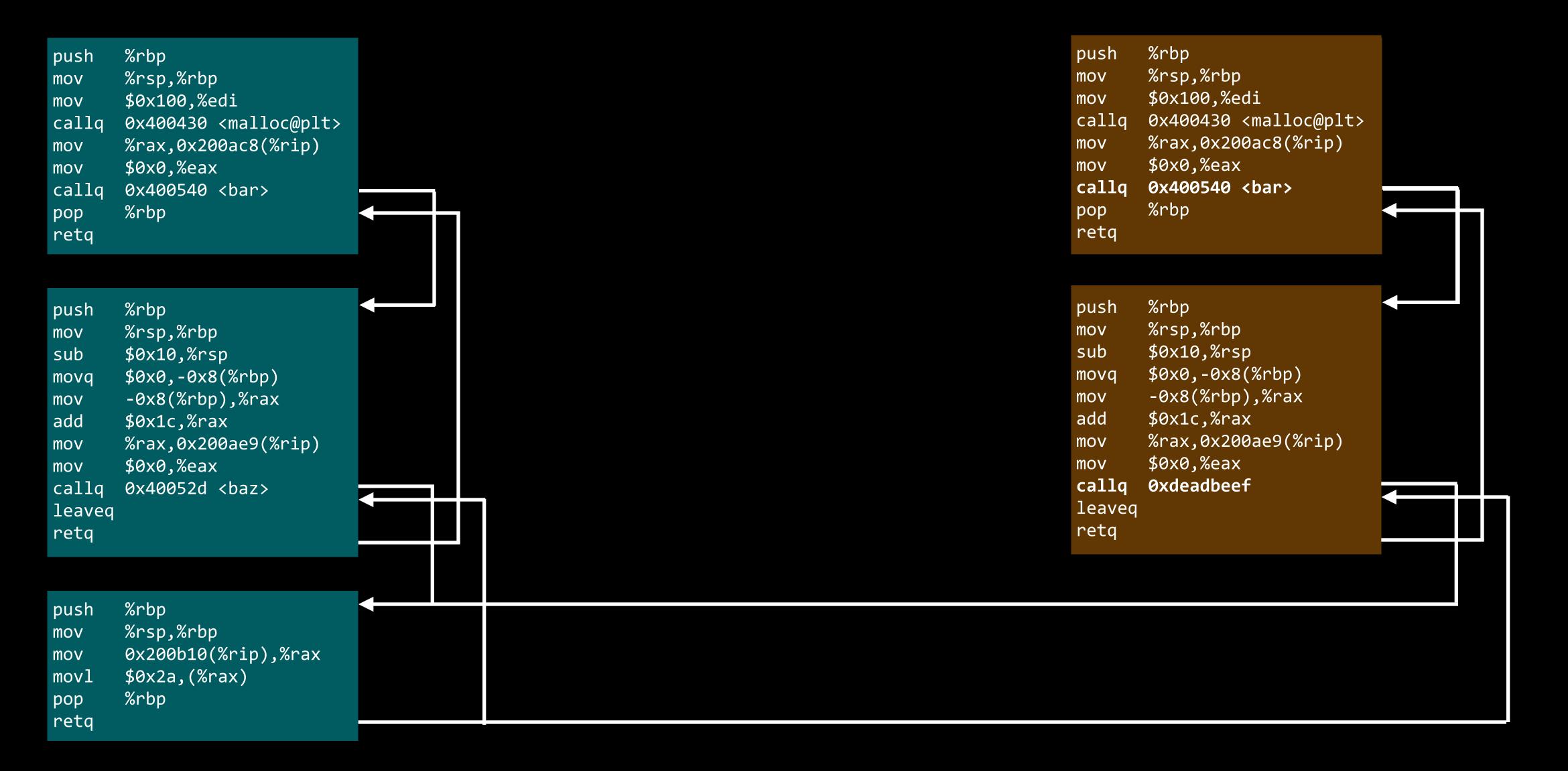

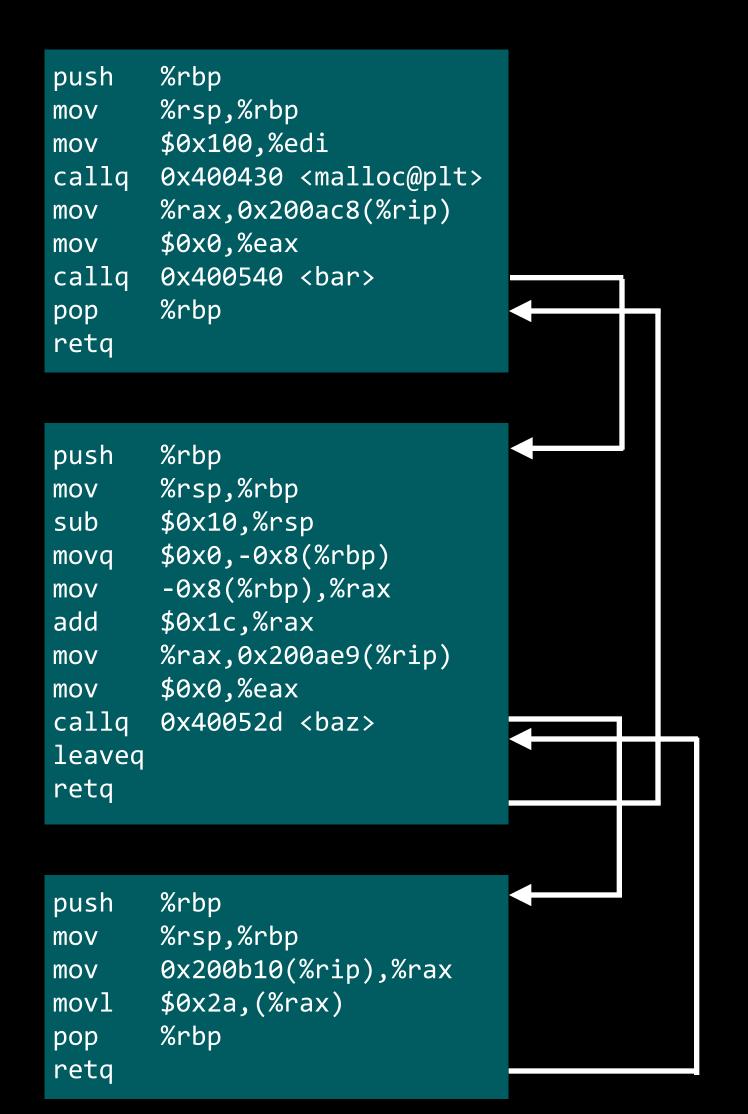

Pin compiles from one ISA directly into the same ISA (e.g., IA32 to IA32, ARM to ARM) without going through an intermediate format, and the compiled code is stored in a software-based code cache. Only code residing in the code cache is executed—the original code is never executed. An application is compiled one trace at

a time. A trace is a straight-line sequence of instructions which terminates at one of the conditions: (i) an unconditional control transfer (branch, call, or return), (ii) a pre-defined number of conditional control transfers, or (iii) a pre-defined number of instructions have been fetched in the trace. In addition to the last exit, a trace may have multiple side-exits (the conditional control transfers). Each exit initially branches to a stub, which re-directs the control to the VM. The VM determines the target address (which is statically unknown for indirect control transfers), generates a new trace for the target if it has not been generated before, and resumes the execution at the target trace.

In the rest of this section, we discuss the following features of our JIT: trace linking, register re-reallocation, and instrumentation optimization. Our current performance effort is focusing on IA32, EM64T, and Itanium, which have all these features implemented. While the ARM version of Pin is fully functional, some of the optimizations are not yet implemented.

### 3.3.2 Trace Linking

To improve performance, Pin attempts to branch directly from a trace exit to the target trace, bypassing the stub and VM. We call this process trace linking. Linking a direct control transfer is straightforward as it has a unique target. We simply patch the branch at the end of one trace to jump to the target trace. However, an indirect control transfer (a jump, call, or return) has multiple possible targets and therefore needs some sort of target-prediction mechanism.

Figure 3(a) illustrates our indirect linking approach as implemented on the x86 architecture. Pin translates the indirect jump into a move and a direct jump. The move puts the indirect target address into register Xedx (this register as well as the Xecx and Xesi shown in Figure 3(a) are obtained via register re-allocation, as we will discuss in Section 3.3.3). The direct jump goes to the first predicted target address 0x40001000 (which is mapped to 0x70001000 in the code cache for this example). We compare %edx against 0x40001000 using the lea/jecxz idiom used in DynamoRIO [6], which avoids modifying the conditional flags register eflags. If the prediction is correct (i.e. %ecr=0), we will branch to match1 to execute the remaining code of the predicted target. If the prediction is wrong, we will try another predicted target 0x40002000 (mapped to 0x70002000 in the code cache). If the target is not found on the chain, we will branch to Lookup Htab\_1, which searches for the target in a hash table (whose base address is "Pin compiles from one ISA directly into the same ISA without going through an intermediate format and stored in a software-based code cache"

"only code residing in the code cache is executed - the original code is never executed."

### Luk et al. Pin: Building Customized Program **Analysis Tools w/ Dynamic Instrumentation**

PLDI '05

mov

sub

mov

mov

add

"Pin compiles from one ISA directly into the same ISA without going through an

recordMemWrite(%rip, -0x8(%rbp)) addl \$0x1, -0x8(%rbp)

-0x8(%rbp), %eax MOV \$0x3, %eax sub %eax, -0x4(%rbp) mov

recordMemWrite(%rip, -0x4(%rbp)) \$0x4(%rbp), %eax MOV

> recordMemWrite(%rip, -0x8(%rbp)) add %eax, -0x8(%rbp)

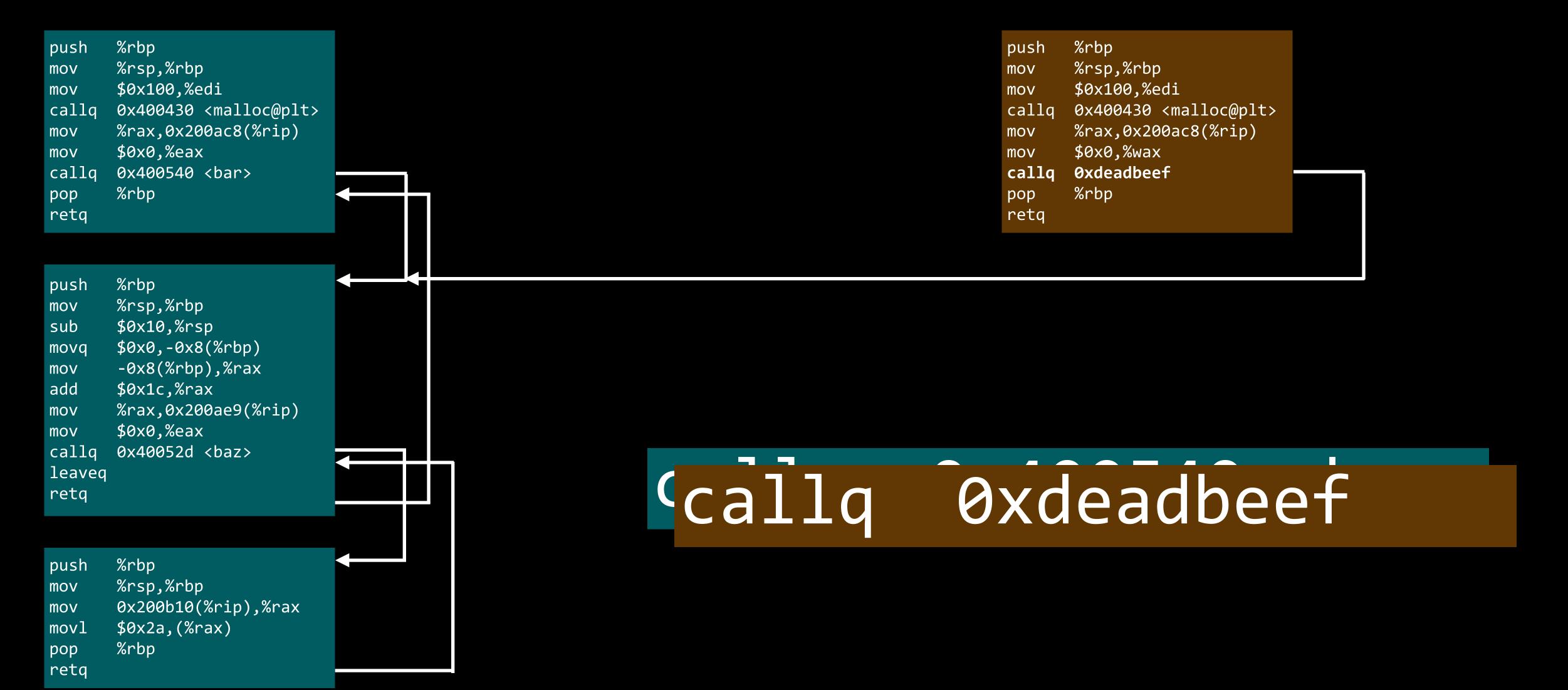

### code rewriting

### jump rewriting

### jump rewriting

### jump rewriting

```

%rbp

push

%rsp,%rbp

mov

$0x100,%edi

mov

callq

0x400430 <malloc@plt>

%rax,0x200ac8(%rip)

mov

$0x0,%eax

mov

0x400540 <bar>

callq

%rbp

pop

retq

%rbp

push

%rsp,%rbp

mov

$0x10,%rsp

sub

$0x0,-0x8(%rbp)

mova

-0x8(%rbp),%rax

mov

add

$0x1c,%rax

%rax,0x200ae9(%rip)

mov

$0x0,%eax

mov

0x40052d <baz>

callq

leaveq

retq

%rbp

push

%rsp,%rbp

mov

0x200b10(%rip),%rax

mov

$0x2a,(%rax)

movl

%rbp

pop

retq

```

### stateless(ish) instrumentation

```

// This routine is executed each time malloc is called.

VOID BeforeMalloc( int size, THREADID threadid )

{

PIN_GetLock(&lock, threadid+1);

fprintf(out, "thread %d entered malloc(%d)\n", threadid, size);

fflush(out);

PIN_ReleaseLock(&lock);

}

```

```

// This function is called before every instruction is executed

VOID docount() { icount++; }

```

PLDI '07

### Valgrind: A Framework for Heavyweight Dynamic Binary Instrumentation

Nicholas Nethercote

National ICT Australia, Melbourne, Australia

njn@csse.unimelb.edu.au

Julian Seward

OpenWorks LLP, Cambridge, UK

julian@open-works.co.uk

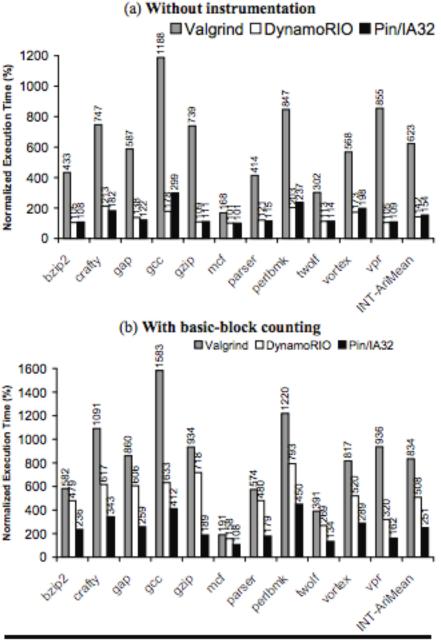

### Abstract

Dynamic binary instrumentation (DBI) frameworks make it easy to build dynamic binary analysis (DBA) tools such as checkers and profilers. Much of the focus on DBI frameworks has been on performance; little attention has been paid to their capabilities. As a result, we believe the potential of DBI has not been fully exploited.

In this paper we describe Valgrind, a DBI framework designed for building heavyweight DBA tools. We focus on its unique support for shadow values—a powerful but previously little-studied and difficult-to-implement DBA technique, which requires a tool to shadow every register and memory value with another value that describes it. This support accounts for several crucial design features that distinguish Valgrind from other DBI frameworks. Because of these features, lightweight tools built with Valgrind run comparatively slowly, but Valgrind can be used to build more interesting, heavyweight tools that are difficult or impossible to build with other DBI frameworks such as Pin and DynamoRIO.

Categories and Subject Descriptors D.2.5 [Software Engineering]: Testing and Debugging—debugging aids, monitors; D.3.4 [Programming Languages]: Processors—incremental compilers

General Terms Design, Performance, Experimentation

Keywords Valgrind, Memcheck, dynamic binary instrumentation, dynamic binary analysis, shadow values

### 1. Introduction

Valgrind is a dynamic binary instrumentation (DBI) framework that occupies a unique part of the DBI framework design space. This paper describes how it works, and how it differs from other frameworks.

### 1.1 Dynamic Binary Analysis and Instrumentation

Many programmers use program analysis tools, such as error checkers and profilers, to improve the quality of their software. Dynamic binary analysis (DBA) tools are one such class of tools; they analyse programs at run-time at the level of machine code.

DBA tools are often implemented using dynamic binary instrumentation (DBI), whereby the analysis code is added to the original code of the client program at run-time. This is convenient for users,

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

PLDI'07 June 11–13, 2007, San Diego, California, USA. Copyright © 2007 ACM 978-1-59593-633-2/07/0006...\$5.00 as no preparation (such as recompiling or relinking) is needed. Also, it gives 100% instrumentation coverage of user-mode code, without requiring source code. Several generic *DBI frameworks* exist, such as Pin [11], DynamoRIO [3], and Valgrind [18, 15]. They provide a base system that can instrument and run code, plus an environment for writing tools that plug into the base system.

The performance of DBI frameworks has been studied closely [1, 2, 9]. Less attention has been paid to their instrumentation capabilities, and the tools built with them. This is a shame, as it is the tools that make DBI frameworks useful, and complex tools are more interesting than simple tools. As a result, we believe the potential of DBI has not been fully exploited.

### 1.2 Shadow Value Tools and Heavyweight DBA

One interesting group of DBA tools are those that use *shadow* values. These tools shadow, purely in software, every register and memory value with another value that says something about it. We call these *shadow* value tools. Consider the following motivating list of shadow value tools; the descriptions are brief but demonstrate that shadow values (a) can be used in a wide variety of ways, and (b) are powerful and interesting.

Memcheck [25] uses shadow values to track which bit values are undefined (i.e. uninitialised, or derived from undefined values) and can thus detect dangerous uses of undefined values. It is used by thousands of C and C++ programmers, and is probably the most widely-used DBA tool in existence.<sup>1</sup>

TaintCheck [20] tracks which byte values are tainted (i.e. from an untrusted source, or derived from tainted values) and can thus detect dangerous uses of tainted values. TaintTrace [6] and LIFT [23] are similar tools.

McCamant and Ernst's secret-tracking tool [13] tracks which bit values are secret (e.g. passwords), and determines how much information about secret inputs is revealed by public outputs.

Hobbes [4] tracks each value's type (determined from operations performed on the value) and can thus detect subsequent operations inappropriate for a value of that type.

DynCompB [7] similarly determines abstract types of byte values, for program comprehension and invariant detection purposes. Annelid [16] tracks which word values are array pointers, and from this can detect bounds errors.

Redux [17] creates a dynamic dataflow graph, a visualisation of a program's entire computation; from the graph one can see all the prior operations that contributed to the each value's creation.

In these tools each shadow value records a simple approximation of each value's history—e.g. one shadow bit per bit, one "which values are undefined (i.e. uninitialised, or derived from undefined values) and can thus detect dangerous uses of undefined values."

"which values are tainted (i.e. from an untrusted source,) and can thus detect dangerous uses of tainted values."

"which word values are array pointers, and from this can detect bounds errors."

<sup>&</sup>lt;sup>1</sup> Purify [8] is a memory-checking tool similar to Memcheck. However, Purify is not a shadow value tool as it does not does not track definedness of values through registers. As a result, it detects undefined value errors less accurately than Memcheck.

PLDI '07

### Valgrind: A Framework for Heavyweight Dynamic Binary Instrumentation

Nicholas Nethercote

National ICT Australia, Melbourne, Australia njn@csse.unimelb.edu.au Julian Seward

OpenWorks LLP, Cambridge, UK julian@open-works.co.uk

### Abstract

Dynamic binary instrumentation (DBI) frameworks make it easy to build dynamic binary analysis (DBA) tools such as checkers and profilers. Much of the focus on DBI frameworks has been on performance; little attention has been paid to their capabilities. As a result, we believe the potential of DBI has not been fully exploited.

In this paper we describe Valgrind, a DBI framework designed for building heavyweight DBA tools. We focus on its unique support for shadow values—a powerful but previously little-studied and difficult-to-implement DBA technique, which requires a tool to shadow every register and memory value with another value that describes it. This support accounts for several crucial design features that distinguish Valgrind from other DBI frameworks. Because of these features, lightweight tools built with Valgrind run comparatively slowly, but Valgrind can be used to build more interesting, heavyweight tools that are difficult or impossible to build with other DBI frameworks such as Pin and DynamoRIO.

Categories and Subject Descriptors D.2.5 [Software Engineering]: Testing and Debugging—debugging aids, monitors; D.3.4 [Programming Languages]: Processors—incremental compilers

General Terms Design, Performance, Experimentation

Keywords Valgrind, Memcheck, dynamic binary instrumentation, dynamic binary analysis, shadow values

### 1. Introduction

Valgrind is a dynamic binary instrumentation (DBI) framework that occupies a unique part of the DBI framework design space. This paper describes how it works, and how it differs from other frameworks.

### 1.1 Dynamic Binary Analysis and Instrumentation

Many programmers use program analysis tools, such as error checkers and profilers, to improve the quality of their software. Dynamic binary analysis (DBA) tools are one such class of tools; they analyse programs at run-time at the level of machine code.

DBA tools are often implemented using dynamic binary instrumentation (DBI), whereby the analysis code is added to the original code of the client program at run-time. This is convenient for users,

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

PLDI'07 June 11–13, 2007, San Diego, California, USA.

Copyright © 2007 ACM 978-1-59593-633-2/07/0006...\$5.00

as no preparation (such as recompiling or relinking) is needed. Also, it gives 100% instrumentation coverage of user-mode code, without requiring source code. Several generic *DBI frameworks* exist, such as Pin [11], DynamoRIO [3], and Valgrind [18, 15]. They provide a base system that can instrument and run code, plus an environment for writing tools that plug into the base system.

The performance of DBI frameworks has been studied closely [1, 2, 9]. Less attention has been paid to their instrumentation capabilities, and the tools built with them. This is a shame, as it is the tools that make DBI frameworks useful, and complex tools are more interesting than simple tools. As a result, we believe the potential of DBI has not been fully exploited.

### 1.2 Shadow Value Tools and Heavyweight DBA

One interesting group of DBA tools are those that use shadow values. These tools shadow, purely in software, every register and memory value with another value that says something about it. We call these shadow value tools. Consider the following motivating list of shadow value tools; the descriptions are brief but demonstrate that shadow values (a) can be used in a wide variety of ways, and (b) are powerful and interesting.

Memcheck [25] uses shadow values to track which bit values are undefined (i.e. uninitialised, or derived from undefined values) and can thus detect dangerous uses of undefined values. It is used by thousands of C and C++ programmers, and is probably the most widely-used DBA tool in existence.<sup>1</sup>

TaintCheck [20] tracks which byte values are tainted (i.e. from an untrusted source, or derived from tainted values) and can thus detect dangerous uses of tainted values. TaintTrace [6] and LIFT [23] are similar tools.

McCamant and Ernst's secret-tracking tool [13] tracks which bit values are secret (e.g. passwords), and determines how much information about secret inputs is revealed by public outputs.

Hobbes [4] tracks each value's type (determined from operations performed on the value) and can thus detect subsequent operations inappropriate for a value of that type.

DynCompB [7] similarly determines abstract types of byte values, for program comprehension and invariant detection purposes.

Annelid [16] tracks which word values are array pointers, and from this can detect bounds errors.

Redux [17] creates a dynamic dataflow graph, a visualisation of a program's entire computation; from the graph one can see all the prior operations that contributed to the each value's creation.

In these tools each shadow value records a simple approximation of each value's history—e.g. one shadow bit per bit, one

One interesting group of DBA tools are those that use shadow values. These tools shadow, purely in software, every register and memory value with another value that says something about it. We call these shadow value tools.

<sup>&</sup>lt;sup>1</sup> Purify [8] is a memory-checking tool similar to Memcheck. However, Purify is not a shadow value tool as it does not does not track definedness of values through registers. As a result, it detects undefined value errors less accurately than Memcheck.

Oxc00000 <value> <value> <value> <value> <value> <value> <value> <value> <value> 0x08048002 <value> 0x08048001 <value> 0x08048000 <value>

| 0xc00000   | <value></value> |

|------------|-----------------|

|            | <value></value> |

| -          | <value></value> |

| _          | <value></value> |

| _          | <value></value> |

|            | <value></value> |

|            | <value></value> |

|            | <value></value> |

|            | <value></value> |

| 0x08048002 | <value></value> |

| 0x08048001 | <value></value> |

| 0x08048000 | <value></value> |

| <metadata></metadata> | 0xc00000   |

|-----------------------|------------|

| <metadata></metadata> |            |

| <metadata></metadata> | 0x08048002 |

| <metadata></metadata> | 0x08048001 |

| <metadata></metadata> | 0x08048000 |

PLDI '07

### Valgrind: A Framework for Heavyweight Dynamic Binary Instrumentation

Nicholas Nethercote National ICT Australia, Melbourne, Australia

njn@csse.unimelb.edu.au

Julian Seward OpenWorks LLP, Cambridge, UK julian@open-works.co.uk

### Abstract

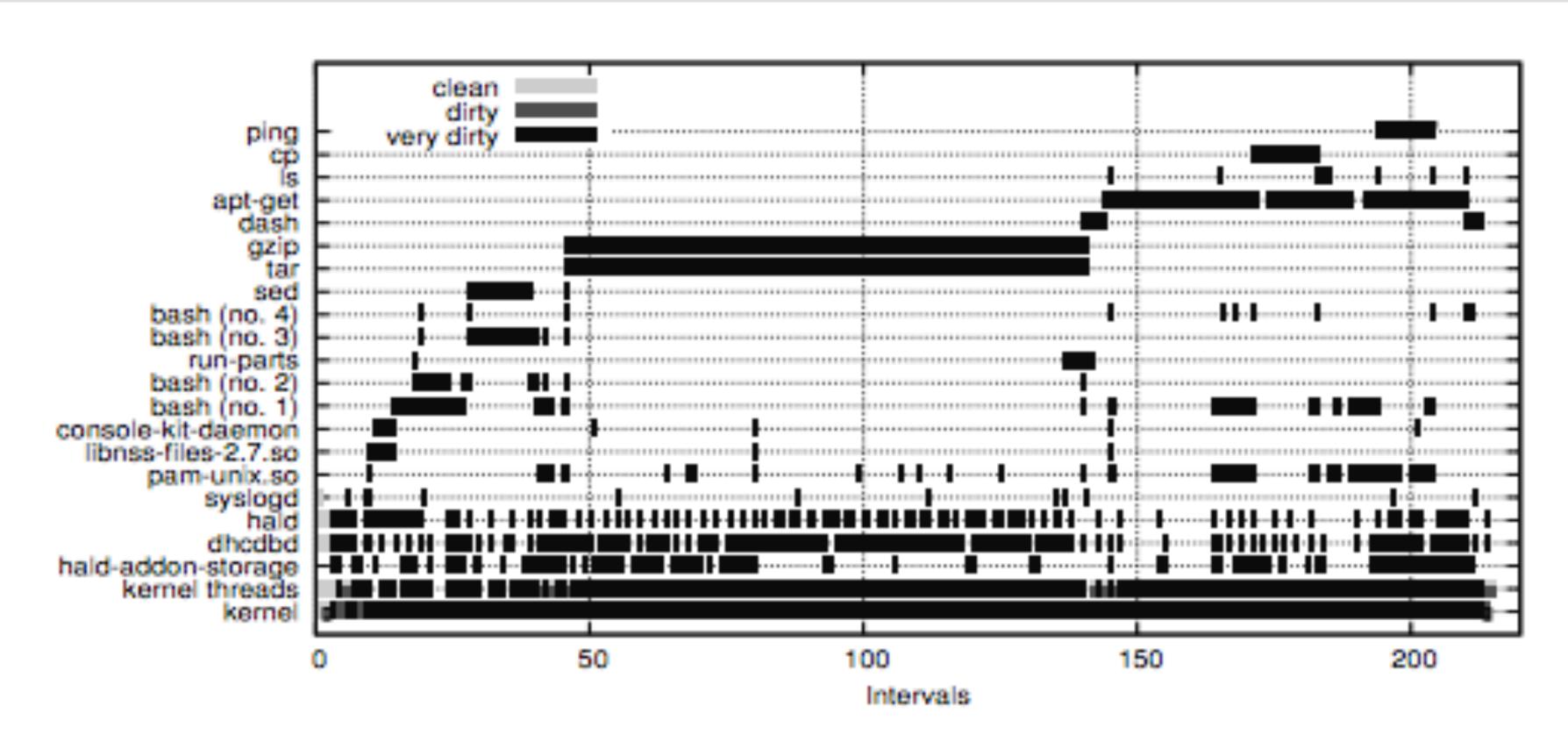

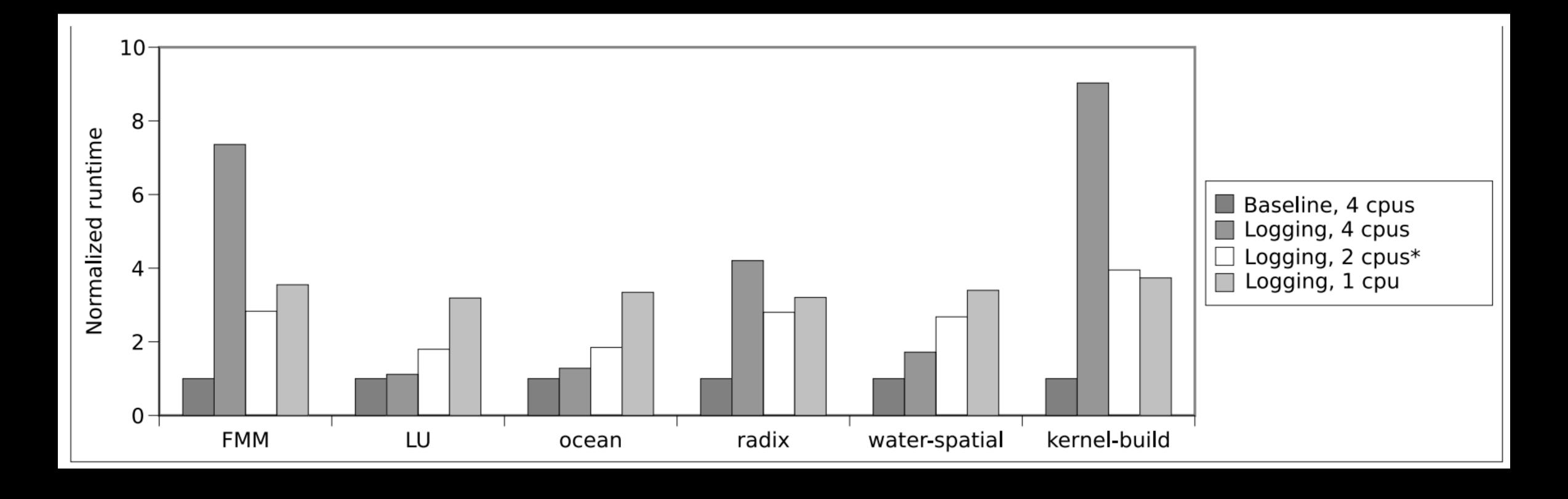

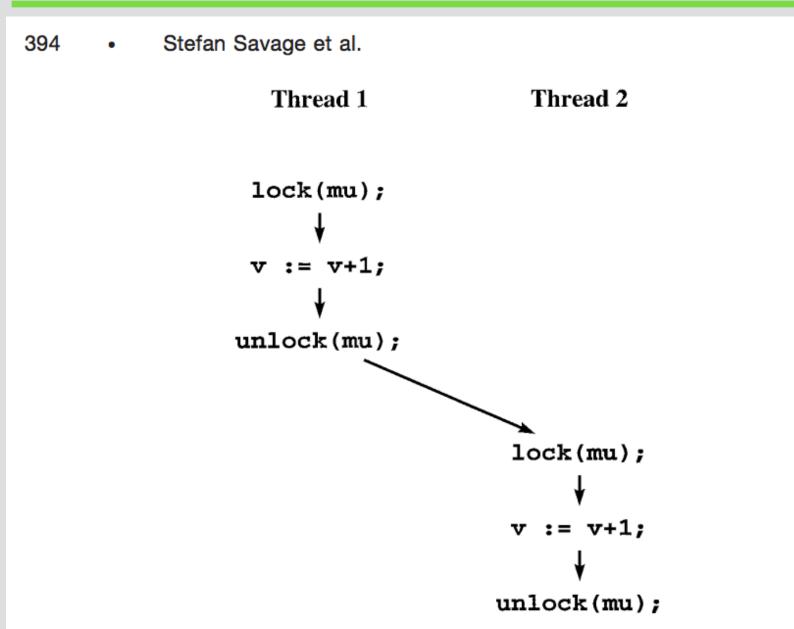

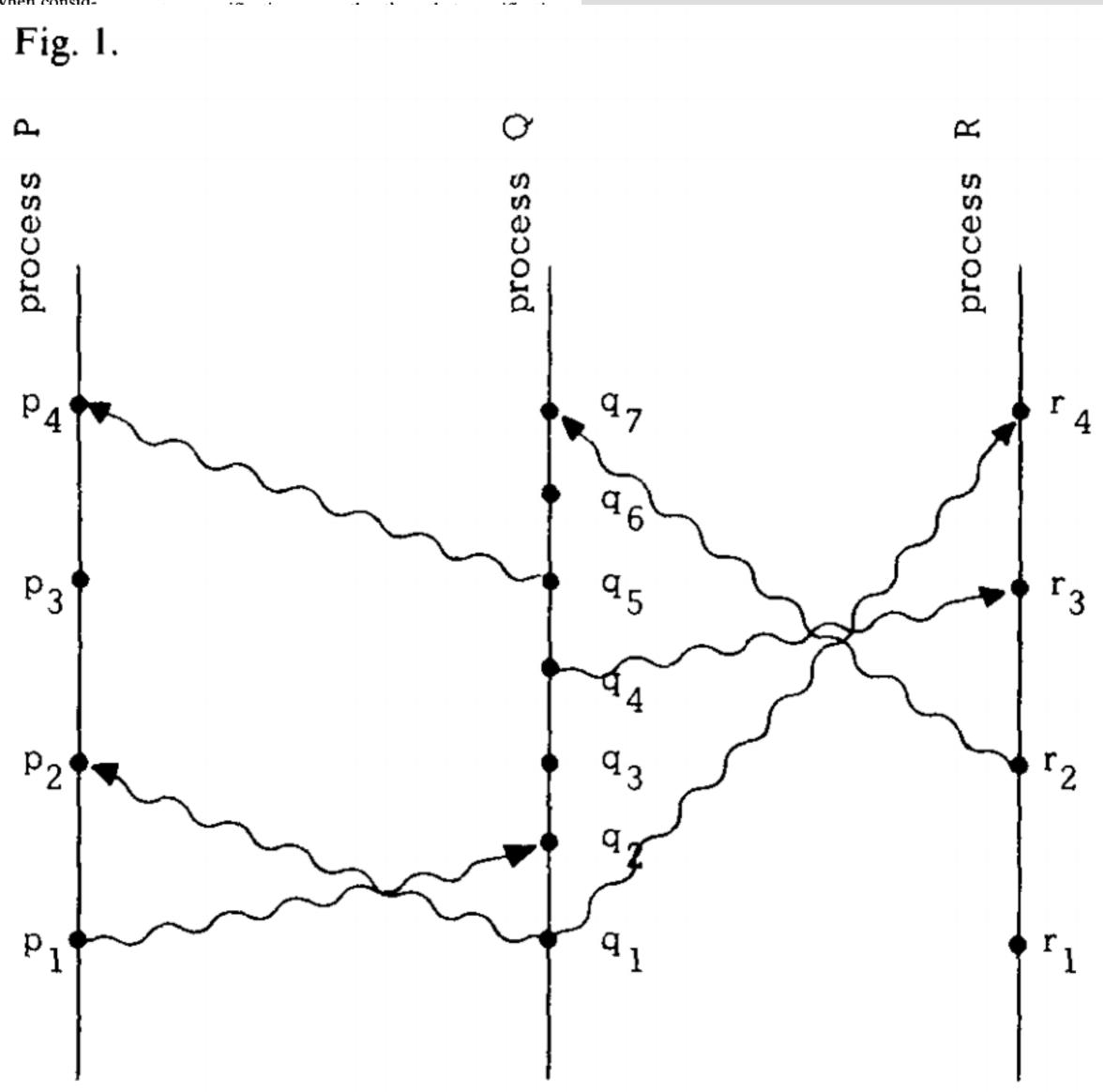

Dynamic binary instrumentation (DBI) frameworks make it easy to build dynamic binary analysis (DBA) tools such as checkers and profilers. Much of the focus on DBI frameworks has been on performance; little attention has been paid to their capabilities. As a